30.1 Introduction

...

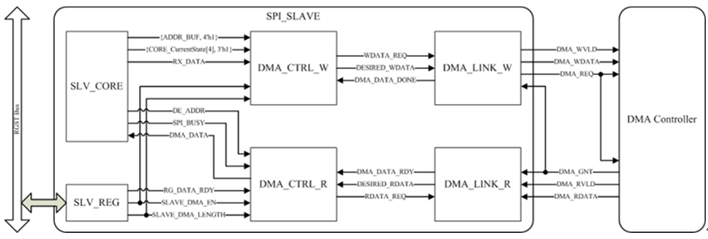

- MST_CORE: Receive or transmit data from or to SPI_SLAVE

- DMA_CTRL_W: Receive DATA from MST_CORE and produce WDATA_REQ with transmit 4-byte data to DMA_LINK_W

- DMA_CTRL_R: Transmit DATA to MST_CORE and produce RDATA_REQ with receive 4-byte data from DMA_LINK_R

- DMA_LINK_R/W: Communicate with DMA_CTRL via proprietary System Bus (SBUS) protocol

Figure 30-4 SPI Slave DMA Function Block

...

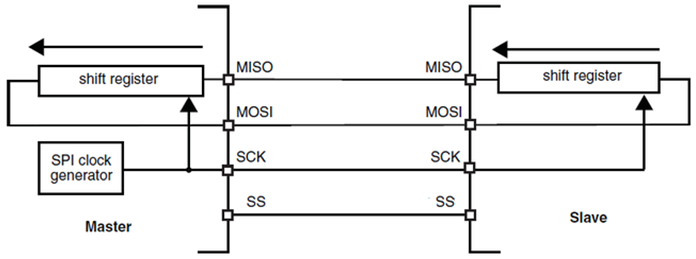

The SPI support full-duplex communication. In this configuration, the shift registers of master and slave are linked using two unidirectional lines between the MOSI and the MISO pins. During SPI communication, data is shifted synchronously on the SCK clock edges provided by the master. The master transmits the data to be sent to the slave via the MOSI line and receives data from the slave via the MISO line. When the data frame transfer is complete the information between the master and slave is exchanged. Figure 30-6 shows one master and one slave device connected status.

Figure 30-6 One master and one slave communication

...

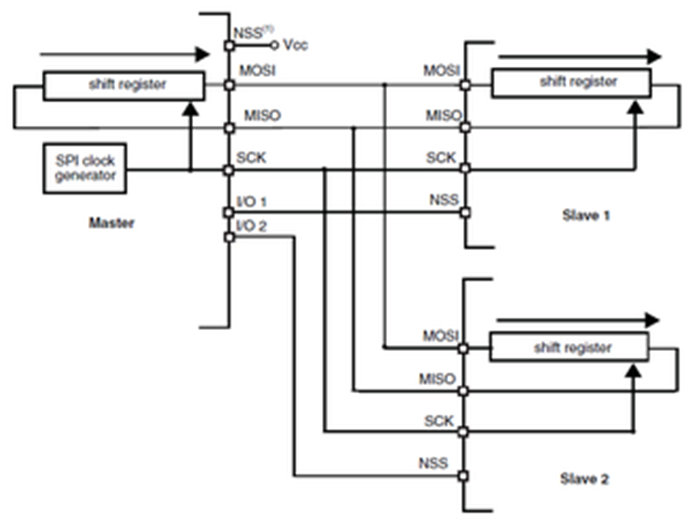

In a configuration with two or more independent slaves, the master uses GPIO pins to manage the chip select lines for each slave (refer to Figure 30-7). The master must select one of the slaves individually by pulling low the GPIO connected to the slave SS input. When this is done, a standard master and dedicated slave communication is established.

Figure 30-7 Master and two independent slaves

...

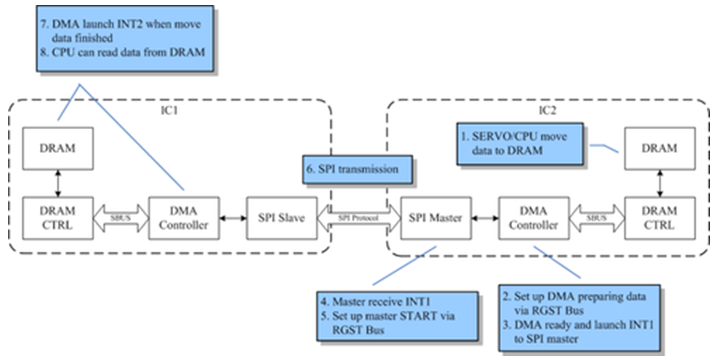

30.13.3 SPI DMA Write Mode Flow

Figure 30-9 SPI DMA Write Mode Flow

...

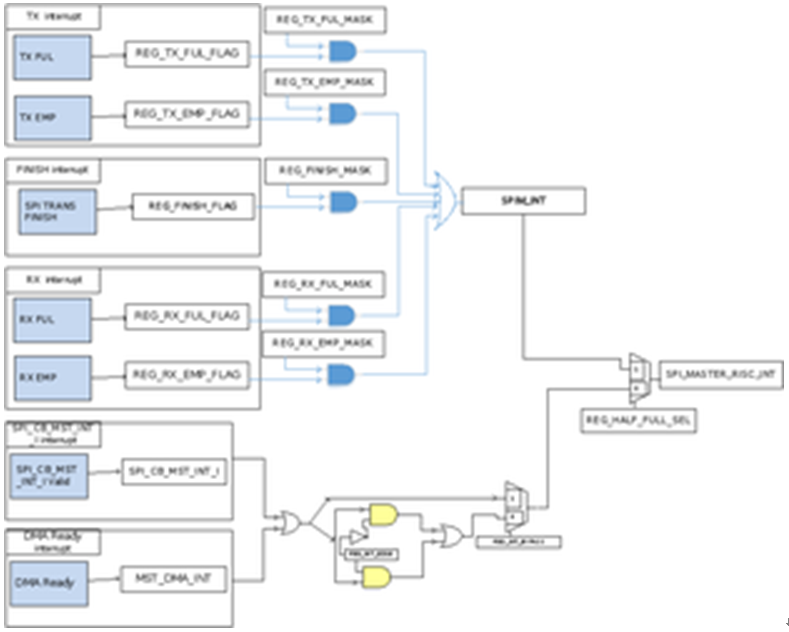

TX and RX FIFO have full and empty interrupt that can be used in burst mode for full duplex master. When tx fifo empty and rx fifo full interrupt received and transfer have not completed, IRQ handler should move data to or fetch data from tx/rx fifo to continue transfer until it complete.Finish int means SPI Transmission done for full duplex master. IRQ handler can handle the data transferred and start a new transmission for full duplex master.SPI_MASTER_RISC_INT (Group91.19 bit7) is generated from SPI_MST_INT_I and MST_DMA_INT. Set INT_EDGE (Group91.19 bit5) register or INT_BYPASS (Group91.19 bit3) register to configure interrupt. SPI_MST_INT_I Interrupt is issued when incoming SPI interrupt to SPI MASTER. MST_DMA_INT interrupt is issued when DMA data is ready (MST_DMA_DATA_RDY). IRQ handler will immediately set up master START via RGST bus and start SPI transmission.

Figure 30-10 SPI MASTER RISC INT

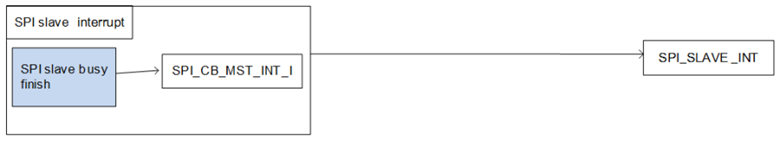

SPI_ SLAVE_INT (Group92.17 bit9) interrupt is issued when SPI slave is not busy. IRQ handler can get data transferred and start a new transmission.

Figure 30-11 SPI SLAVE INT

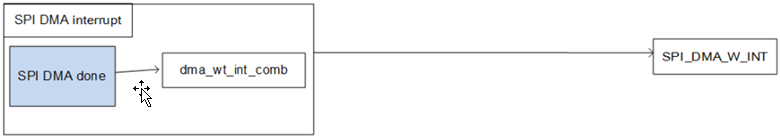

SPI_DMA_W_INT (Group91.20 bit8) interrupt is issued when SPI DMA data transfer is done. IRQ handler can read data from DRAM.

Figure 30-12 SPI DMA W INT

...