30.1 Introduction

...

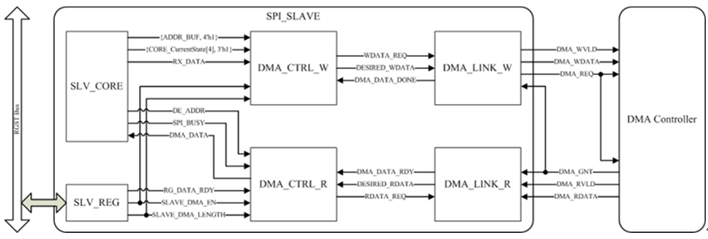

- MST_CORE: Receive or transmit data from or to SPI_SLAVE

- DMA_CTRL_W: Receive DATA from MST_CORE and produce WDATA_REQ with transmit 4-byte data to DMA_LINK_W

- DMA_CTRL_R: Transmit DATA to MST_CORE and produce RDATA_REQ with receive 4-byte data from DMA_LINK_R

- DMA_LINK_R/W: Communicate with DMA_CTRL via proprietary System Bus (SBUS) protocol

Figure 30-4 SPI Slave DMA Function Block

...

Table 30-1 SPI Register Memory Map

All SPIs' registers have the same offset (address - base address) in corresponding SPI register group. Only SPI0 Master and Slave registers are described in following register description, for other SPIs (SPI1, 2, 3) please refer to SPI0 description for more detail.

...

SPI Register Description RGST Table Group 91 SPI MASTER 0

91.0 Transmit register1 (tx data addr)

Address: 0x9C002D80Reset0x9C002D80

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:20 | RO | Reserved |

ADDR | 19:0 | RW | Address for SPI master to transmit in write/ read action |

...

91.2 Transmit register3 (tx data7 6 5 4)

Address: 0x9C002D88Reset0x9C002D88

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

TX DATA 5 | 15:8 | RW | Byte5 data for SPI master to transmit in write action |

TX DATA 4 | 7:0 | RW | Byte4 data for SPI master to transmit in write action |

...

91.9 Receive register1 (rx data3 2 1 0)

Address: 0x9C002DA4Reset0x9C002DA4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RX DATA 3 | 31:24 | RO | Byte3 data that SPI master receive in read action |

RX DATA 2 | 23:16 | RO | Byte2 data that SPI master receive in read action |

RX DATA 1 | 15:8 | RO | Byte1 data that SPI master receive in read action |

RX DATA 0 | 7:0 | RO | Byte0 data that SPI master receive in read action |

...

91.10 Receive register2 (rx data7 6 5 4)

Address: 0x9C002DA8Reset0x9C002DA8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RX DATA 7 | 31:24 | RO | Byte7 data that SPI master receive in read action |

RX DATA 6 | 23:16 | RO | Byte6 data that SPI master receive in read action |

RX DATA 5 | 15:8 | RO | Byte5 data that SPI master receive in read action |

RX DATA 4 | 7:0 | RO | Byte4 data that SPI master receive in read action |

...

91.11 Receive register3 (rx data11 10 9 8)

Address:0x9C002DAC

Reset: 0x0000 0000

...

Field Name | Bit | Access | Description |

RX DATA 15 | 31:24 | RO | Byte15 data that SPI master receive in read action |

RX DATA 14 | 23:16 | RO | Byte14 data that SPI master receive in read action |

RX DATA 13 | 15:8 | RO | Byte13 data that SPI master receive in read action |

RX DATA 12 | 7:0 | RO | Byte12 data that SPI master receive in read action |

91.13 rx/tx fifo data out/in register for full duplex (fifo_data)

Address: 0x9C002DB4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

fifo_data | 31:0 | RO | rx/tx fifo data out/in register for full duplex |

91.14 spi master status for full duplex (spi_status)

Address: 0x9C002DB8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

REG_TOTAL_LENGTH_FD | 31:24 | RW | Total length for full duplex |

REG_TX_LENGTH_FD | 23:16 | RW | TX length for full duplex |

REG_RX_CNT | 15:12 | RO | RX FIFO CNT for full duplex |

REG_TX_CNT | 11:8 | RO | TX FIFO CNT for full duplex |

REG_SPI_BUSY_FD | 7 | RO | SPI_BUSY for full duplex |

REG_FINISH_FLAG | 6 | WO | FINISH_FLAG for full duplex |

REG_RX_FUL_FLAG | 5 | RO | RX_FIFO_FUL_FLAG for full duplex |

REG_RX_EMP_FLAG | 4 | RO | RX_FIFO_EMP_FLAG for full duplex |

REG_TX_FUL_FLAG | 3 | RO | TX_FIFO_FUL_FLAG for full duplex |

REG_TX_EMP_FLAG | 2 | RO | TX_FIFO_EMP_FLAG for full duplex |

REG_MASTER_SW_RST | 1 | RO | SW RST for full duplex |

REG_SPI_START_FD | 0 | RO | SPI START for full duplex |

91.15 spi master config for full duplex (spi_config)

Address: 0x9C002DBC

Reset: 0x0000 0000

...

91.17 SPI master control and clock select register (spi ctrl clk sel)

Address: 0x9C002DC4Reset0x9C002DC4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

R DLY | 31:30 | RW | Additional delay in read action0x0: No delay(default)0x1: Delay 0.5*SPI clk cycle0x2: Delay 1*SPI clk cycle0x3: Delay 1.5*SPI clk cycle |

SPI CLOCK SEL | 29:16 | RW | Ratio between SPI clk and sysclk1/(2*(CLK SEL+1)) |

Reserve | 15:9 | RW | Reserved |

ADDR BIT NUM | 8:7 | RW | Transfer address bit number0x0: 12-bit0x1: 12-bit0x2: 16-bit0x3: 20-bit |

WRITE SAMPLING EDGE | 6 | RW | SPI TX edge |

READ SAMPLING EDGE | 5 | RW | SPI RX edge |

EN POLARITY | 4 | RW | SPI CS polarity |

READ POLARITY | 3 | RW | Read/Write bit polarity |

RW POSITION | 2 | RW | Read/Write bit position |

SB SELECT | 1 | RW | LSB enable in SPI transmission |

SPISTART | 1 | WO | SPI transmission start |

...

91.18 SPI transmission byte No. register (byte no)

Address: 0x9C002DC8Reset0x9C002DC8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:5 | RO | Reserved |

BYTE NO | 4:0 | RW | No. of bytes in SPI transmission Support from 1-byte to 16-byte |

...

91.19 SPI master interrupt control register (spi int busy)

Address: 0x9C002DCC

Reset: 0x0000 0020

...

91.20 SPI master DMA control register (master dma ctrl)

Address: 0x9C002DD0Reset0x9C002DD0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:9 | RO | RESERVED |

DMA W INT STATUS | 8 | RO | DMA Write interrupt statusWhether DMA transmission is finished or not. |

DMA W INT CLR | 7 | RW | 1: Clear DMA write interruptit will return to 0 automatically when interrupt is low. |

DMA RW SEL | 6 | RW | DMA read/write select0: DMA write to DRAM(default)1: DMA read from DRAM MASTER |

DMA BANK | 5 | RW | DRAM bank select0x0: Bank A(default)0x1: Bank B |

MASTER DMA BP WBE | 4 | RWRW | SBUS write-byte enable select0: With write-byte-enable(default)1: No write-byte-enable Used in Legacy SBUS protocol, not supported any more. Left default value without change. |

MASTER DMA BURST | 3:2 | SBUS command select0x0: 4 bytes command(default)0x1: 8 bytes command0x3: A4B4 command others: reserved | |

MASTER MASTER SW RST | 1 | RW | SPI master software reset0: Disable(default)1: Enable |

MASTER DMA EN | 0 | RW | DMA function select0: Disable(default)1: Enable |

...

91.21 SPI master DMA length register (master dma length)

Address: 0x9C002DD4Reset0x9C002DD4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:18 | RO | RESERVED |

MASTER DMA LENGTH | 17:0 | RW | Total data length in DMA transmission (unit:byte) |

91.22 SPI master DMA address register (master dma addr)

Address: 0x9C002DD8Reset0x9C002DD8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

MASTER DMA ADDR | 31:0 | RW | Start address in DRAM to store data (unit:byte) |

...

91.24 SPI master DMA address status register (dma addr status)

Address: 0x9C002DE0Reset0x9C002DE0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

DMA ADDR STATUS | 31:0 | RO | DMA address statusReturn address which DMA access |

...

91.26 Uart DMA control register (uart dma ctrl)

Address:0x9C002DE8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:3 | RO | RESERVED |

UART SW RST | 2 | RW | Software reset when SPI in UART DMA mode |

UART DMA START | 1 | W1C | DMA transmission start signal from UART 1: DMA transmission start ; it will return to 0 automatically. |

UART DMA EN | 0 | RW | DMA function select from UART 0: Disable(default) 1: Enable |

...

91.28 Reserved (reserved)

Address: 0x9C002DF0Reset0x9C002DF0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | RO | Reserved for Internal usage purpose |

...

91.29 Reserved (Reserved)

Address: 0x9C002DF4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | RO | Reserved for Internal usage purpose |

...

91.30 SPI extra cycle control register (spi extra cycle ctrl)

Address: 0x9C002DF8Reset0x9C002DF8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:4 | RO | RESERVED |

SPI EXTRA CYCLE | 3:2 | RW | Choose the number of SPI extra cycle.These settings take effect ONLY when SPI EXTRA CYCLE EN=1'b1 0x0: Add extra 1 SPI cycle(default) 0x1: Add extra 2 SPI cycle 0x2: Add extra 3 SPI cycle 0x3: Add extra 4 SPI cycle |

SPI EN CUT | 1 | RW | SPI EN output interval selectThis setting takes effect ONLY when SPI EXTRA CYCLE EN=1'b1 0: SPI EN output interval will be SPI read plus SPI extra cycle.(default) 1: SPI EN output interval will be as same as SPI read. |

SPI EXTRA CYCLE EN | 0 | RW | Enable SPI extra cycle to fixpath delay in SPI read pro- cess 0: Disable(default) 1: Enable |

...

91.31DMA data ready register (dma data ready)

Address: 0x9C002DFCReset0x9C002DFC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:1 | RO | RESERVED |

MST DMA DATA RDY | 0 | RO | DMA Read data pre-fetch ready |

RGST Table Group 92 SPI SLAVE0

92.0 SPI slave transmit data register1 (tx data2 1 0)

Address: 0x9C002E00Reset0x9C002E00

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RESERVED | 31:24 | RO | RESERVED |

TX DATA 2 | 23:16 | RW | Byte2 data for SPI slave to transmit in read action |

TX DATA 1 | 15:8 | RW | Byte1 data for SPI slave to transmit in read action |

TX DATA 0 | 7:0 | RW | Byte0 data for SPI slave to transmit in read action |

92.1SPI slave transmit data register2 (tx data6 5 4 3)

Address: 0x9C002E04Reset0x9C002E04

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

TX DATA 6 | 31:24 | RW | Byte6 data for SPI slave to transmit in read action |

TX DATA 5 | 23:16 | RW | Byte5 data for SPI slave to transmit in read action |

TX DATA 4 | 15:8 | RW | Byte4 data for SPI slave to transmit in read action |

TX DATA 3 | 7:0 | RW | Byte3 data for SPI slave to transmit in read action |

...

92.4 SPI slave transmit data register5 (tx data15)

Address: 0x9C002E10Reset 0x9C002E10

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RESERVED | 31:8 | RO | RESERVED |

TX DATA 15 | 7:0 | RW | Byte15 data for SPI slave to transmit in read action |

...

92.9 SPI slave receive data register1 (rx data3 2 1 0)

Address: 0x9C002E24Reset 0x9C002E24

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RX DATA 3 | 31:24 | RO | Byte3 data that SPI slave receive in write action |

RX DATA 2 | 23:16 | RO | Byte2 data that SPI slave receive in write action |

RX DATA 1 | 15:8 | RO | Byte1 data that SPI slave receive in write action |

RX DATA 0 | 7:0 | RO | Byte0 data that SPI slave receive in write action |

...

92.10 SPI slave receive data register2 (rx data7 6 5 4)

Address: 0x9C002E28Reset 0x9C002E28

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RX DATA 7 | 31:24 | RO | Byte7 data that SPI slave receive in write action |

RX DATA 6 | 23:16 | RO | Byte6 data that SPI slave receive in write action |

RX DATA 5 | 15:8 | RO | Byte5 data that SPI slave receive in write action |

RX DATA 4 | 7:0 | RO | Byte4 data that SPI slave receive in write action |

...

92.11 SPI slave receive data register3 (rx data11 10 9 8)

Address: 0x9C002E2C

Reset: 0x0000 0000

...

92.17 SPI slave interrupt register (risc int data rdy)

Address: 0x9C002E44Reset 0x9C002E44

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RESERVED | 31:10 | RO | RESERVED |

SPI SLAVE INT | 9 | RO | SPI Slave Interrupt RegisterSPI slave will launch INT to CPU when SPI transmission is finished no matter write or read action. |

SLAVE INT CLR | 8 | RW | SPI slave INT clear1: Clear SPI slave interruptit will return to 0 automatically when interrupt is low. |

RESERVED | 7:1 | RO | RESERVED |

SLAVE DATA RDY | 0 | RW | SPI slave data ready signal1: SPI slave data is ready and launch INT to SPI master. It will return to 0 automatically. |

...

92.18 SPI slave DMA control register (slave dma ctrl)

Address: 0x9C002E48Reset 0x9C002E48

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RESERVED | 31:7 | RO | RESERVED |

SLAVE DMA RW SEL | 6 | RW | SLAVE DMA read/write select 0: DMA write to DRAM(default) 1: DMA read from DRAM |

SLAVE DMA BANK | 5 | RW | DRAM bank select 0: Bank A(default) 1: Bank B |

SLAVE DMA BP WBE | 4 | RW | SBUS write-byte enable select 0: With write-byte-enable(default) 1: No write-byte-enable |

SLAVE DMA BURST | 3:2 | RW | SBUS command select 0x0: 4 bytes command(default) 0x1: 8 bytes command 0x3: A4B4 command |

SLAVE SLAVE SW RST | 1 | RW | SPI slave software reset 0: Disable(default) 1: Enable |

SLAVE DMA EN | 0 | RW | DMA function select 0: Disable(default) 1: Enable |

...

92.19 SPI slave DMA length register (slave dma length)

Address: 0x9C002E4C

Reset: 0x0000 0000

...

92.20 SPI slave DMA address register (slave dma addr)

Address:0x9C002E50Reset0x9C002E50

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

SLAVE DMA ADDR | 31:0 | RW | Slave Mode DMA Start Address |

...

92.23 SPI slave index signal register (addr spi busy)

Address: 0x9C002E5C

Reset: 0x0000 0000

...

92.24 Reserved (Reserved)

Address: 0x9C002E60Reset 0x9C002E60

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

RESERVED | 31:0 | RO | RESERVED |

...