...

GPIO: General purpose I/O

MPP: Multiplex Peripheral Pins

FBIO: FPGA Bus I/O Interface

LCDIF: LCD Interface

HDMIDDC: HDMI Display Data Channel

O: Mean support

X: Mean no support

GPIO_Px_xx: The “x” means port number, so P0 means port0. The “xx” means bit number, so 00 means bit0, and so on.1

Pin Name | Pin No | GPIO | MPP | FBIO | LCDIF | HDMIDDC |

GPIO_P0_00 | 174 | O | X | X | X | X |

GPIO_P0_01 | 175 | O | X | X | X | X |

GPIO_P0_02 | 176 | O | X | O | X | X |

GPIO_P0_03 | 1 | O | X | O | X | X |

GPIO_P0_04 | 2 | O | X | O | X | X |

GPIO_P0_05 | 3 | O | X | O | X | X |

GPIO_P0_06 | 5 | O | X | O | X | X |

GPIO_P0_07 | 6 | O | X | O | X | X |

GPIO_P1_00 | 7 | O | O | O | X | X |

GPIO_P1_01 | 8 | O | O | O | X | X |

GPIO_P1_02 | 9 | O | O | O | X | X |

GPIO_P1_03 | 10 | O | O | O | X | X |

GPIO_P1_04 | 11 | O | O | O | O | X |

GPIO_P1_05 | 12 | O | O | O | O | X |

GPIO_P1_06 | 13 | O | O | O | O | X |

GPIO_P1_07 | 14 | O | O | O | O | X |

GPIO_P2_00 | 15 | O | O | O | O | X |

GPIO_P2_01 | 16 | O | O | O | O | X |

GPIO_P2_02 | 17 | O | O | O | O | X |

GPIO_P2_03 | 18 | O | O | O | O | X |

GPIO_P2_04 | 19 | O | O | O | O | X |

GPIO_P2_05 | 20 | O | O | O | O | X |

GPIO_P2_06 | 21 | O | O | O | O | X |

GPIO_P2_07 | 22 | O | O | O | O | X |

GPIO_P3_00 | 25 | O | O | O | O | X |

GPIO_P3_01 | 26 | O | O | O | O | X |

GPIO_P3_02 | 27 | O | O | O | O | X |

GPIO_P3_03 | 28 | O | O | O | O | X |

GPIO_P3_04 | 29 | O | O | O | O | X |

GPIO_P3_05 | 30 | O | O | O | O | X |

GPIO_P3_06 | 31 | O | O | O | O | X |

GPIO_P3_07 | 32 | O | O | O | O | X |

GPIO_P4_00 | 37 | O | O | O | O | X |

GPIO_P4_01 | 38 | O | O | O | O | X |

GPIO_P4_02 | 39 | O | O | O | O | X |

GPIO_P4_03 | 40 | O | O | O | O | X |

GPIO_P4_04 | 41 | O | O | O | O | X |

GPIO_P4_05 | 42 | O | O | O | O | X |

GPIO_P4_06 | 43 | O | O | O | O | X |

GPIO_P4_07 | 44 | O | O | O | O | X |

GPIO_P5_00 | 47 | O | O | O | X | X |

GPIO_P5_01 | 48 | O | O | O | X | X |

GPIO_P5_02 | 49 | O | O | O | X | X |

GPIO_P5_03 | 50 | O | O | X | X | X |

GPIO_P5_04 | 51 | O | O | X | X | X |

GPIO_P5_05 | 52 | O | O | X | X | X |

GPIO_P5_06 | 53 | O | O | X | X | X |

GPIO_P5_07 | 54 | O | O | X | X | X |

GPIO_P6_00 | 62 | O | O | X | X | X |

GPIO_P6_01 | 63 | O | O | X | X | X |

GPIO_P6_02 | 64 | O | O | X | X | X |

GPIO_P6_03 | 65 | O | O | X | X | X |

GPIO_P6_04 | 66 | O | O | X | X | X |

GPIO_P6_05 | 67 | O | O | X | X | X |

GPIO_P6_06 | 68 | O | O | X | X | X |

GPIO_P6_07 | 69 | O | O | X | X | X |

GPIO_P7_00 | 70 | O | O | X | X | X |

GPIO_P7_01 | 71 | O | O | X | X | X |

GPIO_P7_02 | 72 | O | O | X | X | X |

GPIO_P7_03 | 73 | O | O | X | X | X |

GPIO_P7_04 | 74 | O | O | X | X | O |

GPIO_P7_05 | 75 | O | O | X | X | O |

GPIO_P7_06 | 76 | O | O | X | X | O |

GPIO_P7_07 | 77 | O | O | X | X | O |

GPIO_P8_00 | 80 | O | O | X | X | X |

GPIO_P8_01 | 81 | O | O | X | X | X |

GPIO_P8_02 | 82 | O | O | X | X | X |

GPIO_P8_03 | 83 | O | O | X | X | O |

GPIO_P8_04 | 84 | O | O | X | X | O |

GPIO_P8_05 | 85 | O | O | X | X | O |

GPIO_P8_06 | 86 | O | O | X | X | O |

GPIO_P8_07 | 87 | O | O | X | X | X |

...

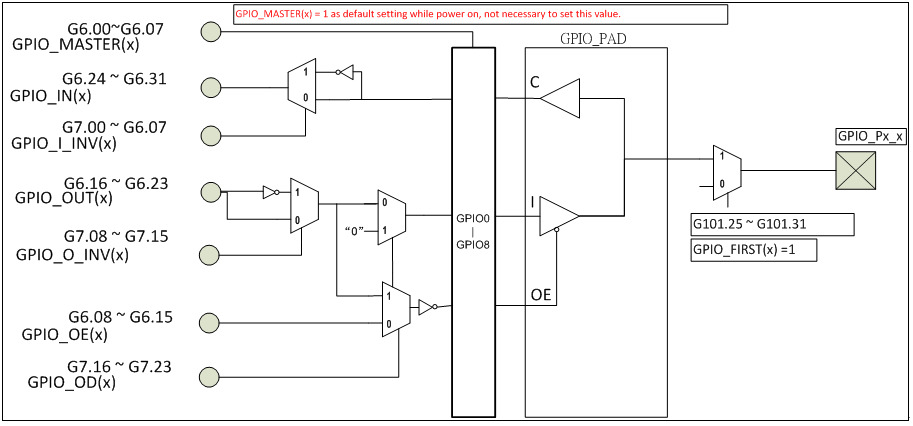

Group101.25~31 (abbreviation as G101.25~31) registers are used for set GPIO_FIRST (for pad control, “1” means GPIO, “0” means Multiplex function ) state. Each bit map to one pin. For example, G101.25[0] control GPIO_P0_00 pin’s GPIO_FIRST state.

Figure 4. Pin Assignment

...

5-1 GPIO Block Diagram

5.3.1. Set General Purpose I/O Pin Method

First step is setting GPIO_MASTER bit to “1”, it means source select as GPIO or IOP(8051).

...

GPIO_P0 port default set as GPIO function.

...

5.3.2. GPIO control method

For example, set GPIO_P0_00 as output without open drain, please set as below:

Action | Step |

Set GPIO_P0_00 as output without open drain | Step1 : G7.16=0x00010000h 0x00010000 , OD = 0 (set bit0 as 0) Step2 : G6.16=0x00010001h 0x00010001 , OUT = 1 (set bit0 as 1) Step3 : G6.08=0x00010001h 0x00010001 , OE = 1 (set bit0 as 1) |

For example, set GPIO_P1_00 as output with open drain, please set as below:

Action | Step |

Set GPIO_P1_00 as output with open drain | Step1 : G7.16=0x01000100h 0x01000100 , OD =1 (set bit8 as 1) Step2 : G6.16=0x01000100h 0x01000100 , OUT = 1 (set bit8 as 1) Step3 : G6.08 OE = X (don’t care) |

...

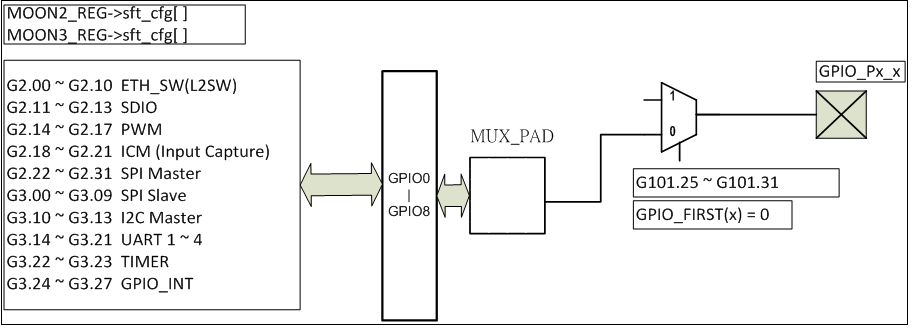

5.4. How to program Multiplex Peripheral Pins

All Multiplex Peripheral Pins support means that you can set all Multiplex Peripheral Pin output through GPIO1 ~ GPIO8 ports. Multiplex Peripheral Pins include: ETH_SW, SDIO, PWM, Input Capture, SPI MASTER, SPI SLAVE, I2C MASTER, UART(1~4), TIMER, GPIO INT. Multiplex Peripheral Pin hardware block show as below figure.

...

Please notice that user should prevent set several signals in the same pin, one signal only can be assign to one pin.

Figure 5. Pin Assignment

...

-2 Multiplex Peripheral Pin Block Diagram

5.4.1. Set Multiplex Peripheral Pin Method

Just need to set GPIO_FIRST bit to “0” , GPIO_MASTER bit set “X” means don’t care in this case. Regarding registers map, please check 6.3.1 .

For example, set GPIO_P1_00 pin to general purpose I/O function, please set registers values as below:

Multiplex Peripheral Pin | |

G6.0 bit8: GPIO_MASTER | X |

G101.25 bit8: GPIO_FIRST | 0 |

GPIO_P1~8 ports default set as Multiplex Peripheral Pin.

...

5.4.2. Set Multiplex Peripheral Pin - ETHERNET_SWITCH pins

There have 2 ETH_SW ports supported in this chip , Each ETH_SW module have 11pins, user can select any signals output in any pins of GPIO_P1~8. The registers G2.0~G2.10 can be used for select ETH_SW signals and pins.

...

ETH_SW0 function | Value | GPIO pins map |

G2.0[7~0] L2SW_CLK_OUT | 43 | GPIO_P6_02 |

G2.0[15~8] L2SW_MAC_SMI_MDC | 37 | GPIO_P5_04 |

G2.1[7~0] L2SW_LED_FLASH0 | 47 | GPIO_P6_06 |

G2.2[7~0] L2SW_LED_ON0 | 38 | GPIO_P5_05 |

G2.3[7~0] L2SW_MAC_SMI_MDIO | 36 | GPIO_P5_03 |

G2.3[15~8] L2SW_P0_MAC_RMII_TXEN | 46 | GPIO_P6_05 |

G2.4[7~0] L2SW_P0_MAC_RMII_TXD0 | 44 | GPIO_P6_03 |

G2.4[15~8] L2SW_P0_MAC_RMII_TXD1 | 45 | GPIO_P6_04 |

G2.5[7~0] L2SW_P0_MAC_RMII_CRSDV | 40 | GPIO_P5_07 |

G2.5[15~8] L2SW_P0_MAC_RMII_RXD0 | 41 | GPIO_P6_00 |

G2.6[7~0] L2SW_P0_MAC_RMII_RXD1 | 42 | GPIO_P6_01 |

G2.6[15~8] L2SW_P0_MAC_RMII_RXER | 39 | GPIO_P5_06 |

...

5.4.3. Set Multiplex Peripheral Pin - SDIO pins

Method same as 65.4.2.

For example, set SDIO port to GPIO_P8_01~06 pins.

SDIO function | Value | GPIO pins map |

G2.11[7~0] SDIO_CLK | 60 | GPIO_P8_03 |

G2.11[15~8] SDIO_CMD | 61 | GPIO_P8_04 |

G2.12[7~0] SDIO_D0 | 59 | GPIO_P8_02 |

G2.12[15~8] SDIO_D1 | 58 | GPIO_P8_01 |

G2.13[7~0] SDIO_D2 | 63 | GPIO_P8_06 |

G2.13[15~8] SDIO_D3 | 62 | GPIO_P8_05 |

...

5.4.4. Set Multiplex Peripheral Pin - PWM pins

Method same as 65.4.2.

For example, set PWM0~3 to GPIO_P3_04~07 pins.

PWM function | Value | GPIO pins map |

G2.14[7~0] PWM0 | 21 | GPIO_P3_04 |

G2.14[15~8] PWM1 | 22 | GPIO_P3_05 |

G2.15[7~0] PWM2 | 23 | GPIO_P3_06 |

G2.15[15~8] PWM3 | 24 | GPIO_P3_07 |

...

5.4.5. Set Multiplex Peripheral Pin - Input Capture pins

Method same as 65.4.2.

For example, set ICM0~1 to GPIO_P4_00~03 pins.

ICM function | Value | GPIO pins map |

G2.18[7~0] ICM0_D | 25 | GPIO_P4_00 |

G2.18[15~8] ICM1_D | 27 | GPIO_P4_02 |

G2.20[7~0] ICM0_CLK | 26 | GPIO_P4_01 |

G2.20[15~8] ICM1_CLK | 28 | GPIO_P4_03 |

...

5.4.6. Set Multiplex Peripheral Pin - SPI MASTER pins

Method same as 65.4.2.

For example, set SPIM0 to GPIO_P1_06~07 and GPIO_P2_00~02 pins.

SPI MASTER function | Value | GPIO pins map |

G2.22[7~0] SPIM0_INT | 7 | GPIO_P1_06 |

G2.22[15~8] SPIM0_CLK | 8 | GPIO_P1_07 |

G2.23[7~0] SPIM0_EN | 9 | GPIO_P2_00 |

G2.23[15~8] SPIM0_DO | 10 | GPIO_P2_01 |

G2.24[7~0] SPIM0_DI | 11 | GPIO_P2_02 |

...

5.4.7. Set Multiplex Peripheral Pin - I2C MASTER pins

Method same as 65.4.2.

For example, set I2CM0 to GPIO_P3_00~01 pins.

I2C MASTER function | Value | GPIO pins map |

G3.10[7~0] I2CM0_CK | 17 | GPIO_P3_00 |

G3.10[15~8] I2CM0_DAT | 18 | GPIO_P3_01 |

...

5.4.8. Set Multiplex Peripheral Pin - UART pins

Method same as 65.4.2.

For example, set UART1 to GPIO_P1_00~01 pins.

UART1 function | Value | GPIO pins map |

G3.14[7~0] UA1_TX | 1 | GPIO_P1_00 |

G3.14[15~8] UA1_RX | 2 | GPIO_P1_01 |

...

5.4.9. Set Multiplex Peripheral Pin - TIMER_INT pins

Method same as 65.4.2.

For example, set TIMER0~1_INT to GPIO_P4_04~05 pins.

TIMER_INT function | Value | GPIO pins map |

G3.22[7~0] TIMER0_INT | 29 | GPIO_P4_04 |

G3.22[15~8] TIMER1_INT | 30 | GPIO_P4_05 |

...

5.4.10. Set Multiplex Peripheral Pin - GPIO_INT pins

Method same as 65.4.2.

For example, set GPIO_INT0~1 to GPIO_P5_00~01 pins.

TIMER_INT function | Value | GPIO pins map |

G3.24[7~0] GPIO_INT0 | 33 | GPIO_P5_00 |

G3.24[15~8] GPIO_INT1 | 34 | GPIO_P5_01 |

...

5.5. How to program FBIO function

FBIO function mode can be enabled while G1.1 register bit12 set to 1, GPIO_P0_02 ~ GPIO_P5_02 pins will be set to FBIO function for FPGA usage. But the priority is GPIO function > Multiplex Peripheral Pin > FBIO Function. While use FBIO function, do not set GPIO function and Multiplex Peripheral Pin within GPIO_P0_02 ~ GPIO_P5_02 pins.

...

5.6. How to program LCDIF function

LCDIF function mode can be enabled while G1.4 register bit6 set to 1, GPIO_P1_04 ~ GPIO_P4_07 pins will be set to LCDIF function for LCD display usage.

1.7. How to program HDMIDDC function

HDMIDDC function mode can be enabled while G1.1 register bit14 set 1 and bit13 set 0, GPIO_P8_03 ~ GPIO_P8_06 pins will be set to HDMIDDC function for HDMI display data channel communication usage.

HDMIDDC function mode can be enabled while G1.1 register bit14 set 1 and bit13 set 1, GPIO_P7_04 ~ GPIO_P7_07 pins will be set to HDMIDDC function for HDMI display data channel communication usage.

...

Table 4 shows the LCDIF signals description.

Pin Name | Pin No(LQFP176) | LCDIF signals description |

GPIO_P1_04 | 11 | TTL_B[0] |

GPIO_P1_05 | 12 | TTL_B[1] |

GPIO_P1_06 | 13 | TTL_B[2] |

GPIO_P1_07 | 14 | TTL_B[3] |

GPIO_P2_00 | 15 | TTL_B[4] |

GPIO_P2_01 | 16 | TTL_B[5] |

GPIO_P2_02 | 17 | TTL_B[6] |

GPIO_P2_03 | 18 | TTL_B[7] |

GPIO_P2_04 | 19 | TTL_G[0] |

GPIO_P2_05 | 20 | TTL_G[1] |

GPIO_P2_06 | 21 | TTL_G[2] |

GPIO_P2_07 | 22 | TTL_G[3] |

GPIO_P3_00 | 25 | TTL_G[4] |

GPIO_P3_01 | 26 | TTL_G[5] |

GPIO_P3_02 | 27 | TTL_G[6] |

GPIO_P3_03 | 28 | TTL_G[7] |

GPIO_P3_04 | 29 | TTL_R[0] |

GPIO_P3_05 | 30 | TTL_R[1] |

GPIO_P3_06 | 31 | TTL_R[2] |

GPIO_P3_07 | 32 | TTL_R[3] |

GPIO_P4_00 | 37 | TTL_R[4] |

GPIO_P4_01 | 38 | TTL_R[5] |

GPIO_P4_02 | 39 | TTL_R[6] |

GPIO_P4_03 | 40 | TTL_R[7] |

GPIO_P4_04 | 41 | TTL_HSYNC |

GPIO_P4_05 | 42 | TTL_VSYNC |

GPIO_P4_06 | 43 | TTL_DCLK |

GPIO_P4_07 | 44 | TTL_DE |

Table 4. LCDIF signals description

5.7. How to program HDMIDDC function

HDMIDDC function mode can be enabled while G1.1 register bit14 set 1 and bit13 set 0, GPIO_P8_03 ~ GPIO_P8_06 pins will be set to HDMIDDC function for HDMI display data channel communication usage.

HDMIDDC function mode can be enabled while G1.1 register bit14 set 1 and bit13 set 1, GPIO_P7_04 ~ GPIO_P7_07 pins will be set to HDMIDDC function for HDMI display data channel communication usage.

Table 5 shows the HDMIDDC signals description.

Pin Name | Pin No(LQFP176) | G1.1 [14:13] | HDMIDDC signals description |

GPIO_P7_04 | 74 | 3 | HDMIDDC3_HPD |

GPIO_P7_05 | 75 | 3 | HDMIDDC3_CEC |

GPIO_P7_06 | 76 | 3 | HDMIDDC3_SDA |

GPIO_P7_07 | 77 | 3 | HDMIDDC3_SCL |

GPIO_P8_03 | 83 | 2 | HDMIDDC2_HPD |

GPIO_P8_04 | 84 | 2 | HDMIDDC2_CEC |

GPIO_P8_05 | 85 | 2 | HDMIDDC2_SDA |

GPIO_P8_06 | 86 | 2 | HDMIDDC2_SCL |

Table 5. HDMIDDC signals description

5.8. Register Map for Multiplex Pins

Address | Group2 | Byte3 | Byte2 | Byte1 | Byte0 |

|---|---|---|---|---|---|

0x9C00 0100 | G2.0 | X | X | L2SW_MAC_SMI_MDC(0-64) | L2SW_CLK_OUT(0-64) |

0x9C00 0104 | G2.1 | X | X | L2SW_LED_FLASH1(0-64) | L2SW_LED_FLASH0(0-64) |

0x9C00 0108 | G2.2 | X | X | L2SW_LED_ON1(0-64) | L2SW_LED_ON0(0-64) |

0x9C00 010C | G2.3 | X | X | L2SW_P0_MAC_RMII_TXEN(0-64) | L2SW_MAC_SMI_MDIO(0-64) |

0x9C00 0110 | G2.4 | X | X | L2SW_P0_MAC_RMII_TXD1(0-64) | L2SW_P0_MAC_RMII_TXD0(0-64) |

0x9C00 0114 | G2.5 | X | X | L2SW_P0_MAC_RMII_RXD0(0-64) | L2SW_P0_MAC_RMII_CRSDV(0-64) |

0x9C00 0118 | G2.6 | X | X | L2SW_P0_MAC_RMII_RXER(0-64) | L2SW_P0_MAC_RMII_RXD1(0-64) |

0x9C00 011C | G2.7 | X | X | L2SW_P1_MAC_RMII_TXD0(0-64) | L2SW_P1_MAC_RMII_TXEN(0-64) |

0x9C00 0120 | G2.8 | X | X | L2SW_P1_MAC_RMII_CRSDV(0-64) | L2SW_P1_MAC_RMII_TXD1(0-64) |

0x9C00 0124 | G2.9 | X | X | L2SW_P1_MAC_RMII_RXD1(0-64) | L2SW_P1_MAC_RMII_RXD0(0-64) |

0x9C00 0128 | G2.10 | X | X | DAISY_MODE(0-64) | L2SW_P1_MAC_RMII_RXER(0-64) |

0x9C00 012C | G2.11 | X | X | SDIO_CMD(0-64) | SDIO_CLK(0-64) |

0x9C00 0130 | G2.12 | X | X | SDIO_D1(0-64) | SDIO_D0(0-64) |

0x9C00 0134 | G2.13 | X | X | SDIO_D3(0-64) | SDIO_D2(0-64) |

0x9C00 0138 | G2.14 | X | X | PWM1(0-64) | PWM0(0-64) |

0x9C00 013C | G2.15 | X | X | PWM3(0-64) | PWM2(0-64) |

0x9C00 0140 | G2.16 | X | X | PWM5(0-64) | PWM4(0-64) |

0x9C00 0144 | G2.17 | X | X | PWM7(0-64) | PWM6(0-64) |

0x9C00 0148 | G2.18 | X | X | ICM1_D(0-64) | ICM0_D(0-64) |

0x9C00 014C | G2.19 | X | X | ICM3_D(0-64) | ICM2_D(0-64) |

0x9C00 0150 | G2.20 | X | X | ICM1_CLK(0-64) | ICM0_CLK(0-64) |

0x9C00 0154 | G2.21 | X | X | ICM3_CLK(0-64) | ICM2_CLK(0-64) |

0x9C00 0158 | G2.22 | X | X | SPIM0_CLK(0-64) | SPIM0_INT(0-64) |

0x9C00 015C | G2.23 | X | X | SPIM0_DO(0-64) | SPIM0_EN(0-64) |

0x9C00 0160 | G2.24 | X | X | SPIM1_INT(0-64) | SPIM0_DI(0-64) |

0x9C00 0164 | G2.25 | X | X | SPIM1_CEN(0-64) | SPIM1_CLK(0-64) |

0x9C00 0168 | G2.26 | X | X | SPIM1_DI(0-64) | SPIM1_DO(0-64) |

0x9C00 016C | G2.27 | X | X | SPIM2_CLK(0-64) | SPIM2_INT(0-64) |

0x9C00 0170 | G2.28 | X | X | SPIM2_DO(0-64) | SPIM2_CEN(0-64) |

0x9C00 0174 | G2.29 | X | X | SPIM3_INT(0-64) | SPIM2_DI(0-64) |

0x9C00 0178 | G2.30 | X | X | SPIM3_CEN(0-64) | SPIM3_CLK(0-64) |

0x9C00 017C | G2.31 | X | X | SPIM3_DI(0-64) | SPIM3_DO(0-64) |

Table 46. Group2 registers address map

...

Address | Group3 | Byte3 | Byte2 | Byte1 | Byte0 |

|---|---|---|---|---|---|

0x9C00 0180 | G3.0 | X | X | SPI0S_CLK(0-64) | SPI0S_INT(0-64) |

0x9C00 0184 | G3.1 | X | X | SPI0S_DO(0-64) | SPI0S_EN(0-64) |

0x9C00 0188 | G3.2 | X | X | SPI1S_INT(0-64) | SPI0S_DI(0-64) |

0x9C00 018C | G3.3 | X | X | SPI1S_EN(0-64) | SPI1S_CLK(0-64) |

0x9C00 0190 | G3.4 | X | X | SPI1S_DI(0-64) | SPI1S_DO(0-64) |

0x9C00 0194 | G3.5 | X | X | SPI2S_CLK(0-64) | SPI2S_INT(0-64) |

0x9C00 0198 | G3.6 | X | X | SPI2S_DO(0-64) | SPI2S_EN(0-64) |

0x9C00 019C | G3.7 | X | X | SPI3S_INT(0-64) | SPI2S_DI(0-64) |

0x9C00 01A0 | G3.8 | X | X | SPI3S_EN(0-64) | SPI3S_CLK(0-64) |

0x9C00 01A4 | G3.9 | X | X | SPI3S_DI(0-64) | SPI3S_DO(0-64) |

0x9C00 01A8 | G3.10 | X | X | I2CM0_DAT(0-64) | I2CM0_CK(0-64) |

0x9C00 01AC | G3.11 | X | X | I2CM1_DAT(0-64) | I2CM1_CK(0-64) |

0x9C00 01B0 | G3.12 | X | X | I2CM2_DAT(0-64) | I2CM2_CK(0-64) |

0x9C00 01B4 | G3.13 | X | X | I2CM3_DAT(0-64) | I2CM3_CK(0-64) |

0x9C00 01B8 | G3.14 | X | X | UA1_RX(0-64) | UA1_TX(0-64) |

0x9C00 01BC | G3.15 | X | X | UA1_RTS(0-64) | UA1_CTS(0-64) |

0x9C00 01C0 | G3.16 | X | X | UA2_RX(0-64) | UA2_TX(0-64) |

0x9C00 01C4 | G3.17 | X | X | UA2_RTS(0-64) | UA2_CTS(0-64) |

0x9C00 01C8 | G3.18 | X | X | UA3_TX(0-64) | UA3_RX(0-64) |

0x9C00 01CC | G3.19 | X | X | UA3_RTS(0-64) | UA3_CTS(0-64) |

0x9C00 01D0 | G3.20 | X | X | UA4_RX(0-64) | UA4_TX(0-64) |

0x9C00 01D4 | G3.21 | X | X | UA4_RTS(0-64) | UA4_CTS(0-64) |

0x9C00 01D8 | G3.22 | X | X | TIMER1_INT(0-64) | TIMER0_INT(0-64) |

0x9C00 01DC | G3.23 | X | X | TIMER3_INT(0-64) | TIMER2_INT(0-64) |

0x9C00 01E0 | G3.24 | X | X | GPIO_INT1(0-64) | GPIO_INT0(0-64) |

0x9C00 01E4 | G3.25 | X | X | GPIO_INT3(0-64) | GPIO_INT2(0-64) |

0x9C00 01E8 | G3.26 | X | X | GPIO_INT5(0-64) | GPIO_INT4(0-64) |

0x9C00 01EC | G3.27 | X | X | GPIO_INT7(0-64) | GPIO_INT6(0-64) |

0x9C00 01F0 | G3.28 | X- | X | X | X |

0x9C00 01F4 | G3.29 | X | X | X | X |

0x9C00 01F8 | G3.30 | X | X | X | X |

0x9C00 01FC | G3.31 | X | X | X | X |

Table 57. Group3 registers address map

...

Address | Group6 | Byte3 | Byte2 | Byte1 | Byte0 |

|---|---|---|---|---|---|

0x9C00 0300 | G6.0 | X | X | GPIO_P1_MASTER | GPIO_P0_MASTER |

0x9C00 0304 | G6.1 | X | X | GPIO_P3_MASTER | GPIO_P2_MASTER |

0x9C00 0308 | G6.2 | X | X | GPIO_P5_MASTER | GPIO_P4_MASTER |

0x9C00 030C | G6.3 | X | X | GPIO_P7_MASTER | GPIO_P6_MASTER |

0x9C00 0310 | G6.4 | X | X | X | GPIO_P8_MASTER |

0x9C00 0314 | G6.5 | X | X | X | X |

0x9C00 0318 | G6.6 | X | X | X | X |

0x9C00 031C | G6.7 | X | X | X | X |

0x9C00 0320 | G6.8 | X | X | GPIO_P1_OE | GPIO_P0_OE |

0x9C00 0324 | G6.9 | X | X | GPIO_P3_OE | GPIO_P2_OE |

0x9C00 0328 | G6.10 | X | X | GPIO_P5_OE | GPIO_P4_OE |

0x9C00 032C | G6.11 | X | X | GPIO_P7_OE | GPIO_P6_OE |

0x9C00 0330 | G6.12 | X | X | X | GPIO_P8_OE |

0x9C00 0334 | G6.13 | X | X | X | X |

0x9C00 0338 | G6.14 | X | X | X | X |

0x9C00 033C | G6.15 | X | X | X | X |

0x9C00 0340 | G6.16 | X | X | GPIO_P1_OUT | GPIO_P0_OUT |

0x9C00 0344 | G6.17 | X | X | GPIO_P3_OUT | GPIO_P2_OUT |

0x9C00 0348 | G6.18 | X | X | GPIO_P5_OUT | GPIO_P4_OUT |

0x9C00 034C | G6.19 | X | X | GPIO_P7_OUT | GPIO_P6_OUT |

0x9C00 0350 | G6.20 | X | X | X | GPIO_P8_OUT |

0x9C00 0354 | G6.21 | X | X | X | X |

0x9C00 0358 | G6.22 | X | X | X | X |

0x9C00 035C | G6.23 | X | X | X | X |

0x9C00 0360 | G6.24 | GPIO_P3_IN | GPIO_P2_IN | GPIO_P1_IN | GPIO_P0_IN |

0x9C00 0364 | G6.25 | GPIO_P7_IN | GPIO_P6_IN | GPIO_P5_IN | GPIO_P4_IN |

0x9C00 0368 | G6.26 | X | X | X | GPIO_P8_IN |

0x9C00 036C | G6.27 | X | X | X | X |

0x9C00 0370 | G6.28 | X | X | X | X |

0x9C00 0374 | G6.29 | X | X | X | X |

Table 68. Group6 registers address map

...

Address | Group7 | Byte3 | Byte2 | Byte1 | Byte0 |

0x9C00 0380 | G7.0 | X | X | GPIO_P1_I_INV | GPIO_P0_I_INV |

0x9C00 0384 | G7.1 | X | X | GPIO_P3_I_INV | GPIO_P2_I_INV |

0x9C00 0388 | G7.2 | X | X | GPIO_P5_I_INV | GPIO_P4_I_INV |

0x9C00 038C | G7.3 | X | X | GPIO_P7_I_INV | GPIO_P6_I_INV |

0x9C00 0390 | G7.4 | X | X | X | GPIO_P8_I_INV |

0x9C00 0394 | G7.5 | X | X | X | X |

0x9C00 0398 | G7.6 | X | X | X | X |

0x9C00 039C | G7.7 | X | X | X | X |

0x9C00 03A0 | G7.8 | X | X | GPIO_P1_O_INV | GPIO_P0_O_INV |

0x9C00 03A4 | G7.9 | X | X | GPIO_P3_O_INV | GPIO_P2_O_INV |

0x9C00 03A8 | G7.10 | X | X | GPIO_P5_O_INV | GPIO_P4_O_INV |

0x9C00 03AC | G7.11 | X | X | GPIO_P7_O_INV | GPIO_P6_O_INV |

0x9C00 03B0 | G7.12 | X | X | X | GPIO_P8_O_INV |

0x9C00 03B4 | G7.13 | X | X | X | X |

0x9C00 03B8 | G7.14 | X | X | X | X |

0x9C00 03BC | G7.15 | X | X | X | X |

0x9C00 03C0 | G7.16 | X | X | GPIO_P1_OD | GPIO_P0_OD |

0x9C00 03C4 | G7.17 | X | X | GPIO_P3_OD | GPIO_P2_OD |

0x9C00 03C8 | G7.18 | X | X | GPIO_P5_OD | GPIO_P4_OD |

0x9C00 03CC | G7.19 | X | X | GPIO_P7_OD | GPIO_P6_OD |

0x9C00 03D0 | G7.20 | X | X | X | GPIO_P8_OD |

0x9C00 03D4 | G7.21 | X | X | X | X |

0x9C00 03D8 | G7.22 | X | X | X | X |

0x9C00 03DC | G7.23 | X | X | X | X |

Table 79. Group7 registers address map

...

Address | Group101 | Byte3 | Byte2 | Byte1 | Byte0 |

|---|---|---|---|---|---|

0x9C00 3280 | G101.0 | X | X | X | X |

0x9C00 3284 | G101.1 | X | X | X | X |

0x9C00 3288 | G101.2 | X | X | X | X |

0x9C00 328C | G101.3 | X | X | X | X |

0x9C00 3290 | G101.4 | X | X | X | X |

0x9C00 3294 | G101.5 | X | X | X | X |

0x9C00 3298 | G101.6 | X | X | X | X |

0x9C00 329C | G101.7 | X | X | X | X |

0x9C00 32A0 | G101.8 | X | X | X | X |

0x9C00 32A4 | G101.9 | X | X | X | X |

0x9C00 32A8 | G101.10 | X | X | X | X |

0x9C00 32AC | G101.11 | X | X | X | X |

0x9C00 32B0 | G101.12 | X | X | X | X |

0x9C00 32B4 | G101.13 | X | X | X | X |

0x9C00 32B8 | G101.14 | X | X | X | X |

0x9C00 32BC | G101.15 | X | X | X | X |

0x9C00 32C0 | G101.16 | X | X | X | X |

0x9C00 32C4 | G101.17 | X | X | X | X |

0x9C00 32C8 | G101.18 | X | X | X | X |

0x9C00 32CC | G101.19 | X | X | X | X |

0x9C00 32D0 | G101.20 | X | X | X | X |

0x9C00 32D4 | G101.21 | X | X | X | X |

0x9C00 32D8 | G101.22 | X | X | X | X |

0x9C00 32DC | G101.23 | X | X | X | X |

0x9C00 32E0 | G101.24 | X | X | X | X |

0x9C00 32E4 | G101.25 | GPIO_P3_FIRST | GPIO_P2_FIRST | GPIO_P1_FIRST | GPIO_P0_FIRST |

0x9C00 32E8 | G101.26 | GPIO_P7_FIRST | GPIO_P6_FIRST | GPIO_P5_FIRST | GPIO_P4_FIRST |

0x9C00 32EC | G101.27 | X | X | X | GPIO_P8_FIRST |

0x9C00 32F0 | G101.28 | X | X | X | X |

0x9C00 32F4 | G101.29 | X | X | X | X |

0x9C00 32F8 | G101.30 | X | X | X | X |

0x9C00 32FC | G101.31 | X | X | X | X |

Table 810. Group101 registers address map

...