1718.1 Introduction

This section describes the SPI_NAND Controller and its function. The SPI_NAND Controller is used to transmit or receive data with SPI_NAND device. The control registers locate at RGST Table Group 87&88 which memory map address are 0x9C002B80~0x9C002BFF. The SPI_NAND controller has below features.

- Support BCH auto encode and decode

- Support 32-bit AXI master bus for transferring data between controller and dram for DMA mode

- Exchange to 32-bit AXI Slave bus from 32-bit OCP bus

- Support auto multi page read

- Support auto multi page program

- Support enable BCH function for DMA mode

- Support SPI_CLK is divided from CLK_SPI, and frequency division coefficient is 1/2, 1/4, 1/6, 1/8, 1/16, 1/24, 1/32

...

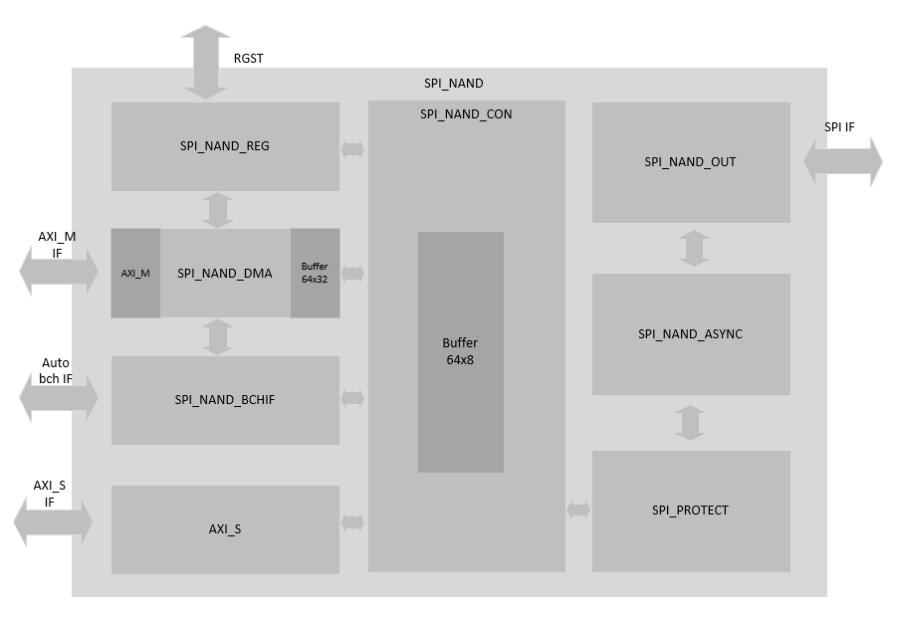

18.2 Function Diagram

A generalized function diagram of SPI_NAND is shown in Figure 1718-1. SPI_PROTECT is reserved for SPI_NAND Controller. SPI_PROTECT function is useful for SPI_NOR controller.

Figure 1718-1 SPINAND Functional Blocks

- SPI_NAND_REG: This block is used for register configure.

- SPI_NAND_DMA: Support 32-bit AXI master bus to read/write data between controller and dram for DMA mode.

- SPI_NAND_CON: This block is used for controlling the operation flow

- SPI_NAND_OUT: SPI interface with external SPI device.

- SPI_NAND_ASYNC: For async information between SPI_NAND_CON and SPI_NAND_OUT

- SPI_NAND_BCHIF: For auto bch function

- SPI_NAND_AXI_S: Exchange to 32-bit AXI Slave bus from 32-bit OCP bus.

...

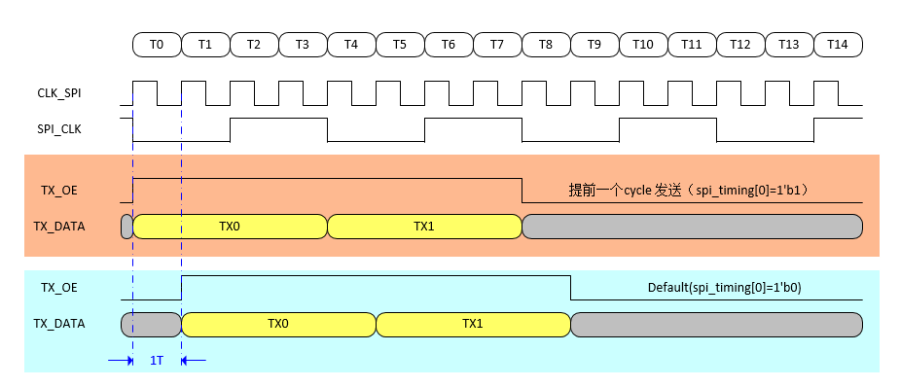

18.3 Data Control Timing

SPI_NAND Controller TX timing: The TX output start timing decides by spi_timing[0] which is bit0 of Group 87.1 spi_timing register. When spi_timing[0]=1 , TX will advance one system clock cycle to send data. Please refer to figure 1718-2.

Figure 1718-2 TX timing chart

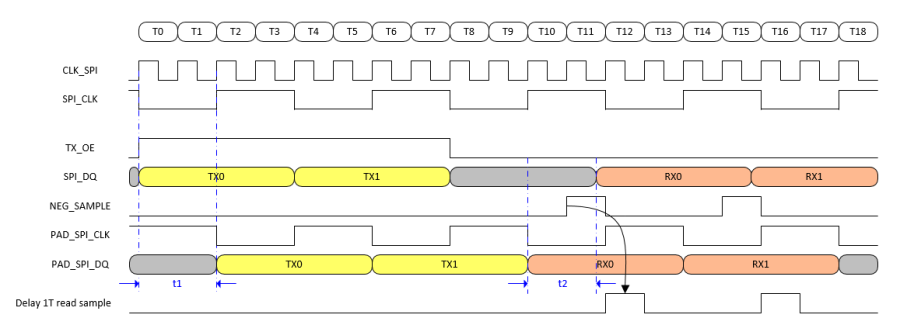

SPI_NAND Controller RX timing: The RX timing can be fine tune by spi_timing[3:1] which is bit[3:1] of Group 87.1 spi_timing register.

- Figure 1718-3 RX timing chart

- If the pad TX delay is t1,than from device to response data until SPI Controller receive data the delay is t2.

- NEG_SAMPLE is spi_controller default sample point

- As above figure,controller can't get correct data in the default sample point,user can fine tune spi_timing[3:1] to get correct read timing. For example, in figure 16-3 set spi_timing[3:1]=1 can get correct sample data.

...

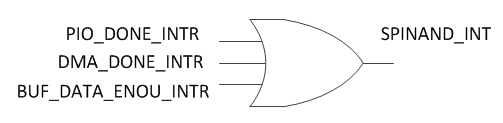

18.4 SPI NAND Interrupts

The SPI_NAND interrupt events are connected to the same interrupt vector, please refer to figure 1718-4. These events generate an interrupt if the corresponding "Mask Bit" isn't set. The mask control register is in Group 87.17. The interrupt status register is in Group 87.18. SPI_NAND controller interrupt is a level signal. It supports three kinds of interrupt status. If one interrupt mask enable, this interrupt will only update the status, the SPINAND_INT will not

| Anchor | ||||

|---|---|---|---|---|

|

Figure 1618-4 SPINAND Interrupt Tree

SPI interrupt status register (Group 87.18 spi_intr_sts) description.

- PIO_DONE_INTR: When PIO mode transfer finished, spi_intr_sts[2] will be high. Software write 1 to clean this bit.

- DMA_DONE_INTR: spi_intr_sts[1] indicate the current dma operation is done. Software can write 1 to clear this bit

- BUF_DATA_ENOU_INTR: spi_intr_sts[0] indicate the number of data received from flash has reached the setting amount. Software can write 1 to clear this bit. The amount is set in spi_cfg0[21] which is bit 21 of Group 87.6 register. Set spi_cfg0[21]=1, the buffer size is 32byte. Set spi_cfg0[21]=0, the buffer size is 64byte.

...

18.5 Registers Map

...

18.5.1 Registers Memory Map

Address | Group No. | Register Name | Description |

|---|---|---|---|

0x9C002B80 | G87.0 | spi ctrl | SPI Control Register |

0x9C002B84 | G87.1 | spi timing | SPI Timing Register |

0x9C002B88 | G87.2 | spi page addr | SPI Page Address Regsister |

0x9C002B8C | G87.3 | spi data | SPI Data Register |

0x9C002B90 | G87.4 | spi status | SPI Status Register |

0x9C002B94 | G87.5 | spi auto cfg | SPI Configuration1 Register |

0x9C002B98 | G87.6 | spi cfg0 | SPI Configuration0 Register |

0x9C002B9C | G87.7 | spi cfg1 | SPI Configuration1 Register |

0x9C002BA0 | G87.8 | spi cfg2 | SPI Configuration2 Register |

0x9C002BA4 | G87.9 | spi data 64 | SPI Data Buffer Regsiter |

0x9C002BA8 | G87.10 | spi buf addr | SPI Buffer Address Register |

0x9C002BAC | G87.11 | spi status 2 | SPI Status2 Register |

0x9C002BB0 | G87.12 | spi err status | SPI Controller Error Status Register |

0x9C002BB4 | G87.13 | mem data addr | Memory Data Address |

0x9C002BB8 | G87.14 | mem parity addr | Memory Data Address |

0x9C002BBC | G87.15 | spi col addr | SPI Column Page Address |

0x9C002BC0 | G87.16 | spi bch | SPI BCH configuration Register |

0x9C002BC4 | G87.17 | spi intr msk | SPI Interrupt Mask Register |

0x9C002BC8 | G87.18 | spi intr sts | SPI Interrupt Status Register |

0x9C002BCC | G87.19 | spi page size | SPI device page size |

...

18.5.2 Registers Description

RGST Table Group 87SPI NAND Controller Registers

...