AUDIO

Introduction

The 【AUD module】is an abbreviation of Audio. This module manages all of the audio playback. It contains the standard I2S and S/PDIF interface (Encode/Decode), signals record from ADC, and multi-channel mix. It supports up to 192KHz sample rate. When the audio data has been decoded by DSP and saved in DRAM, AUD module will fetch the data from DRAM and encode it with I2S or SPDIF protocol. It also can decode the I2s or SPDIF signal and save the data in DRAM for further usage.

Function Diagram

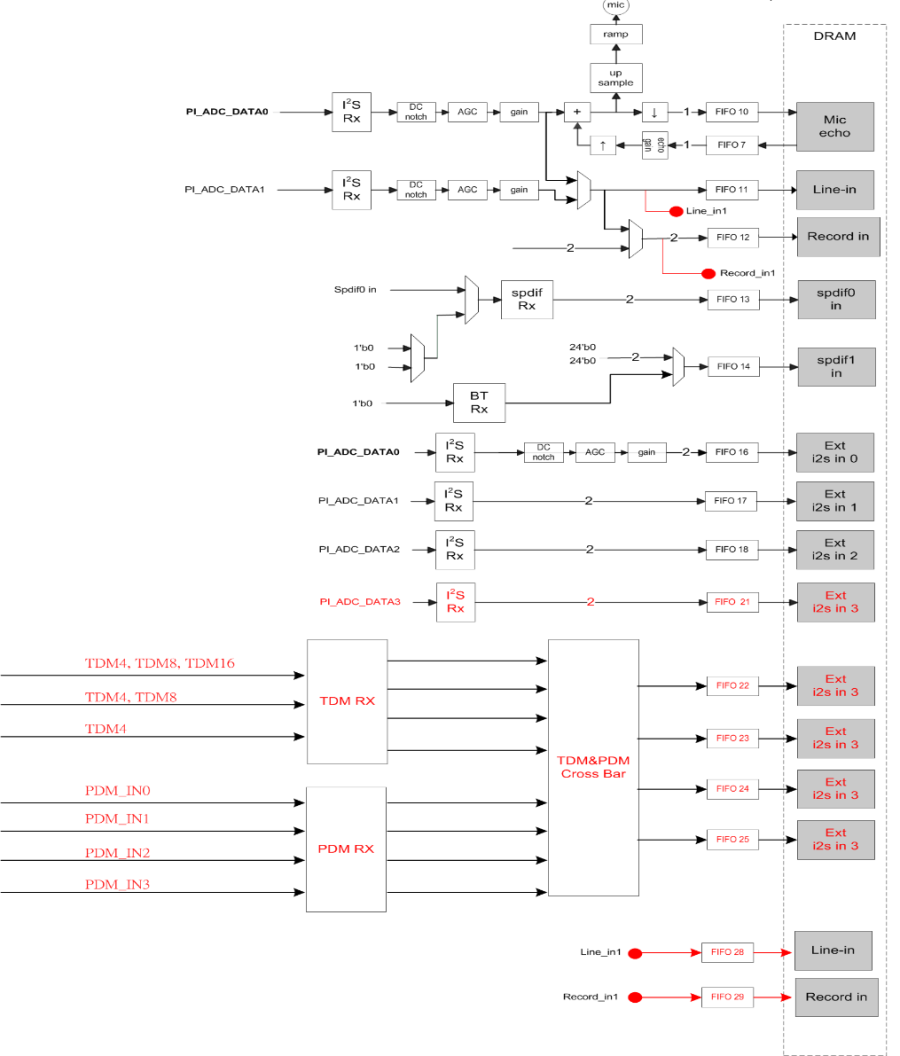

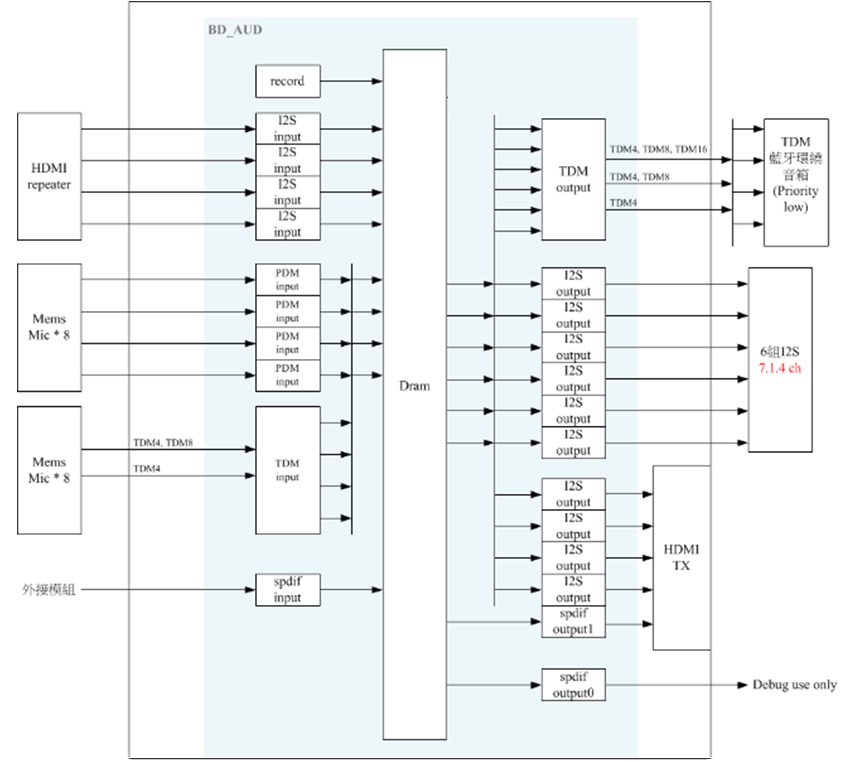

The input path is shown as figure 28-1 and the output path is shown as figure 28-2. The hardware block diagram is shown as figure 28-3..

Figure 28-1 AUD Intput Functional Blocks

Figure 28-2 AUD Output Functional Blocks

Figure 28-3 AUD Hardware Functional Blocks

The I2S output up to 6 stereo channels and input up to 4 stereo channels.

The SPDIF interface support one output and one input.

The TDM/PDM interface support up to 8 channel microphone array.

Pin assignment

GPIO_P1_00 ~ GPIO_P1_06 pins will be set to I2S audio IN function while G1.1 register bit15 set to 1. (Please refer to table 28-1)

GPIO_P2_05 ~ GPIO_P3_05 pins will be set to I2S audio OUT function while G1.2 register bit0 set to 1. (Please refer to table 28-1)

GPIO_P2_04 pin will be set to SPDIF IN function while G1.2 register bit2 set to 1. (Please refer to table 28-2)

GPIO_P2_04 pin will be set to SPDIF OUT function while G1.2 register bit3 set to 1. (Please refer to table 28-2)

GPIO_P2_05 ~ GPIO_P3_02 pins will be set to TDM TX function while G1.2 register bit4 set to 1. (Please refer to table 28-3)

GPIO_P1_07 ~ GPIO_P2_02 pins will be set to TDM RX function while G1.2 register bit5 set to 1. (Please refer to table 28-3)

GPIO_P1_07 ~ GPIO_P2_03 pins will be set to PDM RX function while G1.2 register bit6 set to 1. (Please refer to table 28-4)

GPIO_P3_07 ~ GPIO_P4_04 pins will be set to PCM function while G1.2 register bit7 set to 1. (Please refer to table 28-5)

While use audio function, do not set GPIO function and Multiplex Peripheral Pin within GPIO_P1_00 ~ GPIO_P4_04 pins.

Please also careful that some pins have multiplex functions, don't enable them at the same time.

Pin Name |

I2S audio IN signals |

I2S audio OUT signals |

GPIO_P1_00 |

CLKGENA_EXT_ADC_XCK_O |

|

GPIO_P1_01 |

ADC_BCK |

|

GPIO_P1_02 |

ADC_LRCK |

|

GPIO_P1_03 |

ADC_DATA0 |

|

GPIO_P1_04 |

ADC_DATA1 |

|

GPIO_P1_05 |

ADC_DATA2 |

|

GPIO_P1_06 |

ADC_DATA3 |

|

GPIO_P2_05 |

|

CLKGENA_EXT_DAT_XCK |

GPIO_P2_06 |

|

AU_BCK |

GPIO_P2_07 |

|

AU_LRCK |

GPIO_P3_00 |

|

AU_DATA0 |

GPIO_P3_01 |

|

AU_DATA1 |

GPIO_P3_02 |

|

AU_DATA2 |

GPIO_P3_03 |

|

AU_DATA3 |

GPIO_P3_04 |

|

AU_DATA4 |

GPIO_P3_05 |

|

AU_DATA5 |

Table 28-1 I2C audio pin define

Pin Name |

SPDIF IN signals |

SPDIF OUT signals |

GPIO_P2_04 |

AUD_IEC0_RX |

|

GPIO_P3_06 |

|

AUD_IEC0_TX |

Table 28-2 SPDIF pin define

Pin Name |

TDM TX signals |

TDM RX signals |

GPIO_P2_05 |

CLKGENA_TDMTX_XCK_O |

|

GPIO_P2_06 |

TDMTX_BCK |

|

GPIO_P2_07 |

TDMTX_SYNC |

|

GPIO_P3_00 |

TDMTX_DATA4 |

|

GPIO_P3_01 |

TDMTX_DATA8 |

|

GPIO_P3_02 |

TDMTX_DATA16 |

|

GPIO_P1_07 |

|

TDMRX_BCK |

GPIO_P2_00 |

|

TDMRX_SYNC |

GPIO_P2_01 |

|

TDMRX_DATA4 |

GPIO_P2_02 |

|

TDMRX_DATA8 |

Table 28-3 TDM pin define

Pin Name |

PDM RX signals |

GPIO_P1_07 |

PDMRX_BCK |

GPIO_P2_00 |

PDMRX_DATA0 |

GPIO_P2_01 |

PDMRX_DATA1 |

GPIO_P2_02 |

PDMRX_DATA2 |

GPIO_P2_03 |

PDMRX_DATA3 |

Table 28-4 PDM pin define

Pin Name |

PCM signals |

GPIO_P3_07 |

PCM_IEC_TX0 |

GPIO_P4_00 |

PCM_IEC_TX1 |

GPIO_P4_01 |

PCM_IEC_TX2 |

GPIO_P4_02 |

PCM_IEC_TX3 |

GPIO_P4_03 |

PCM_IEC_TX4 |

GPIO_P4_04 |

PCM_IEC_TX5 |

Table 28-5 PCM pin define

Registers Map

Registers Memory Map

Address |

Group No. |

Register Name |

Description |

0x9C001E00 |

G60.0 |

audif_ctrl |

AUD Interface Control |

0x9C001E04 |

G60.1 |

aud_enable |

Audio FIFO Request Enable |

0x9C001E08 |

G60.2 |

pcm_cfg |

Audio PCM (I2S) Format Configuration |

0x9C001E0C |

G60.3 |

i2s_mute_flag_ctrl |

Mute Flag of I2S TX Module |

0x9C001E10 |

G60.4 |

ext_adc_cfg |

External ADC (I2S) Format Configuration |

0x9C001E14 |

G60.5 |

int_dac_ctrl0 |

Internal DAC Control 0 (ACODEC_CFG0) |

0x9C001E18 |

G60.6 |

int_adc_ctrl |

Internal ADC Config |

0x9C001E1C |

G60.7 |

adc_in_path_switch |

ADC Input Path Switch |

0x9C001E20 |

G60.8 |

int_adc_dac_cfg |

Internal ADC and DAC (I2S) Format Configuration |

0x9C001E24 |

G60.9 |

reserved |

Reserved |

0x9C001E28 |

G60.10 |

iec_cfg |

S/PDIF Configuration |

0x9C001E2C |

G60.11 |

iec0_valid_out |

Valid Bit for S/PDIF TX0 |

0x9C001E30 |

G60.12 |

iec0_par0_out |

Channel Status of S/PDIF TX0 |

0x9C001E34 |

G60.13 |

iec0_par1_out |

Channel Status of S/PDIF TX0 |

0x9C001E38 |

G60.14 |

iec1_valid_out |

Valid Bit for S/PDIF TX1 |

0x9C001E3C |

G60.15 |

iec1_par0_out |

Channel Status of S/PDIF TX1 |

0x9C001E40 |

G60.16 |

iec1_par1_out |

Channel Status of S/PDIF TX1 |

0x9C001E44 |

G60.17 |

iec0_rx_debug_info |

Debug Information of S/PDIF RX0 |

0x9C001E48 |

G60.18 |

iec0_valid_in |

Valid Bit of S/PDIF RX0 |

0x9C001E4C |

G60.19 |

iec0_par0_in |

Channel Status of S/PDIF RX0 |

0x9C001E50 |

G60.20 |

iec0_par1_in |

Channel Status of S/PDIF RX0 |

0x9C001E54 |

G60.21 |

iec1_rx_debug_info |

Debug Information of S/PDIF RX1 |

0x9C001E58 |

G60.22 |

iec1_valid_in |

Valid Bit of S/PDIF RX1 |

0x9C001E5C |

G60.23 |

iec1_par0_in |

Channel Status of S/PDIF RX1 |

0x9C001E60 |

G60.24 |

iec1_par1_in |

Channel Status of S/PDIF RX1 |

0x9C001E64 |

G60.25 |

iec2_rx_debug_info |

Debug Information of S/PDIF RX2 |

0x9C001E68 |

G60.26 |

iec2_valid_in |

Valid Bit of S/PDIF RX2 |

0x9C001E6C |

G60.27 |

iec2_par0_in |

Channel Status of S/PDIF RX2 |

0x9C001E70 |

G60.28 |

iec2_par1_in |

Channel Status of S/PDIF RX2 |

0x9C001E74 |

G60.29 |

reserved |

SACD Channel Number (Reserved) |

0x9C001E78 |

G60.30 |

iec_tx_user_wdata |

IEC Tx User FIFO Data |

0x9C001E7C |

G60.31 |

iec_tx_user_ctrl |

IEC Tx User FIFO Control |

Address |

Group No. |

Register Name |

Description |

0x9C001E80 |

G61.0 |

adcp_ch_enable |

ADCPRC Configuration Group 1 |

0x9C001E84 |

G61.1 |

adcp_fubypass |

ADCPRC Configuration Group 2 |

0x9C001E88 |

G61.2 |

adcp_mode_ctrl |

ADCPRC Mode Control |

0x9C001E8C |

G61.3 |

adcp_init_ctrl |

ADCP Initialization Control |

0x9C001E90 |

G61.4 |

adcp_coeff_din |

Coefficient Data Input |

0x9C001E94 |

G61.5 |

adcp_agc_cfg |

ADCPRC AGC Configuration of Ch0/1 |

0x9C001E98 |

G61.6 |

adcp_agc_cfg2 |

ADCPRC AGC Configuration of Ch2/3 |

0x9C001E9C |

G61.7 |

adcp_gain_0 |

ADCPRC System Gain0 |

0x9C001EA0 |

G61.8 |

adcp_gain_1 |

ADCP System Gain1 |

0x9C001EA4 |

G61.9 |

adcp_gain_2 |

ADCP System Gain2 |

0x9C001EA8 |

G61.10 |

adcp_gain_3 |

ADCP System Gain3 |

0x9C001EAC |

G61.11 |

adcp_risc_gain |

ADCP RISC Gain |

0x9C001EB0 |

G61.12 |

adcp_mic_l |

ADCPRC Microphone - in Left Channel Data |

0x9C001EB4 |

G61.13 |

adcp_mic_r |

ADCPRC Microphone - in Right Channel Data |

0x9C001EB8 |

G61.14 |

adcp_agc_gain |

ADCPRC AGC Gain |

0x9C001EBC |

G61.15 |

reserved |

Reserved |

0x9C001EC0 |

G61.16 |

aud_apt_mode |

Audio Playback Timer Mode |

0x9C001EC4 |

G61.17 |

aud_apt_data |

Audio Playback Timer |

0x9C001EC8 |

G61.18 |

aud_apt_parameter |

Audio Playback Timer Parameter |

0x9C001ECC |

G61.19 |

reserved |

Reserved |

0x9C001ED0 |

G61.20 |

aud_audhwya |

DRAM Base Address Offset |

0x9C001ED4 |

G61.21 |

aud_inc_0 |

DMA Counter Increment/Decrement |

0x9C001ED8 |

G61.22 |

aud_delta_0 |

Delta Value |

0x9C001EDC |

G61.23 |

aud_fifo_enable |

Audio FIFO Enable |

0x9C001EE0 |

G61.24 |

aud_fifo_mode |

FIFO Mode Control |

0x9C001EE4 |

G61.25 |

aud_fifo_support |

Supported FIFOs (Debug Function) |

0x9C001EE8 |

G61.26 |

aud_fifo_reset |

Host FIFO Reset |

0x9C001EEC |

G61.27 |

aud_chk_ctrl |

Checksum Control (Debug Function) |

0x9C001EF0 |

G61.28 |

aud_new_pts |

New PTS |

0x9C001EF4 |

G61.29 |

aud_new_pts_ptr |

FIFO PTR Related to New PTS |

0x9C001EF8 |

G61.30 |

aud_embedded_input_ctrl |

Embedded Input Control (Debug Function) |

0x9C001EFC |

G61.31 |

aud_misc_ctrl |

Miscellaneous Control |

Address |

Group No |

Register Name |

Description |

0x9C001F00 |

G62.0 |

aud_ext_dac_xck_cfg |

External DAC XCK Configuration |

0x9C001F04 |

G62.1 |

aud_ext_dac_bck_cfg |

External DAC BCK Configuration |

0x9C001F08 |

G62.2 |

aud_iec0_bclk_cfg |

S/PDIF TX0 BCLK Configuration |

0x9C001F0C |

G62.3 |

aud_ext_adc_xck_cfg |

External ADC XCK Configuration |

0x9C001F10 |

G62.4 |

aud_ext_adc_bck_cfg |

External ADC BCK Configuration |

0x9C001F14 |

G62.5 |

aud_int_adc_xck_cfg |

Internal ADC XCK Configuration |

0x9C001F18 |

G62.6 |

reserved |

Reserved |

0x9C001F1C |

G62.7 |

aud_int_dac_xck_cfg |

Internal DAC XCK Configuration |

0x9C001F20 |

G62.8 |

aud_int_dac_bck_cfg |

Internal DAC BCK Configuration |

0x9C001F24 |

G62.9 |

aud_iec1_bclk_cfg |

S/PDIF TX1 BCLK Configuration |

0x9C001F28 |

G62.10 |

reserved |

Reserved |

0x9C001F2C |

G62.11 |

aud_pcm_iec_bclk_cfg |

PCM S/PDIF TX BCLK Configuration |

0x9C001F30 |

G62.12 |

aud_xck_osr104_cfg |

Internal DAC XCK OSR104 Configuration |

0x9C001F34 |

G62.13 |

aud_hdmi_tx_mclk_cfg |

HDMI TX MCLK Configuration |

0x9C001F38 |

G62.14 |

aud_hdmi_tx_bclk_cfg |

HDMI TX BCLK Configuration |

0x9C001F3C |

G62.15 |

hdm_tx_pcm_cfg |

HDMI TX PCM (I2S) Format Configuration |

0x9C001F40 |

G62.16 |

hdmi_rx_cfg |

HDMI RX (I2S) Format Configuration |

0x9C001F44 |

G62.17 |

aud_aadc_agc_cfg1 |

DAGC0/1 Config0 |

0x9C001F48 |

G62.18 |

aud_aadc_agc_cfg2 |

DAGC0/1 Config1 |

0x9C001F4C |

G62.19 |

aud_aadc_agc_cfg3 |

DAGC0/1 Config2 |

0x9C001F50 |

G62.20 |

aud_aadc_agc_cfg4 |

DAGC0/1 Config3 |

0x9C001F54 |

G62.21 |

int_adc_ctrl3 |

Internal ADC Config 3 |

0x9C001F58 |

G62.22 |

int_adc_ctrl2 |

Internal ADC Config 2 |

0x9C001F5C |

G62.23 |

int_dac_ctrl2 |

Internal DAC Config 2 |

0x9C001F60 |

G62.24 |

int_dac_ctrl1 |

Internal DAC Config 1 |

0x9C001F64 |

G62.25 |

aud_aadc_agc_cfg0 |

DAGC0/1 Config0 |

0x9C001F68 |

G62.26 |

aud_force_cken |

AUD Force CKEN |

0x9C001F6C |

G62.27 |

aud_recovery_ctrl |

AUD Recovery Control |

0x9C001F70 |

G62.28 |

pcm_iec_par0_out |

Channel Status of PCM S/PDIF TX |

0x9C001F74 |

G62.29 |

pcm_iec_par1_out |

Channel Status of PCM S/PDIF TX and Configurations |

0x9C001F78 |

G62.30 |

dmactrl_cnt_inc_1 |

DMA Counter Increment/Decrement |

0x9C001F7C |

G62.31 |

dmactrl_cnt_delta_1 |

Delta Value |

Address |

Group No |

Register Name |

Description |

0x9C001F80 |

G63.0 |

bt_ifx_cfg |

BlueTooth IFX Config |

0x9C001F84 |

G63.1 |

bt_i2s_cfg |

BT I2S Format Configuration |

0x9C001F88 |

G63.2 |

bt_xck_cfg |

BlueTooth XCK Config |

0x9C001F8C |

G63.3 |

bt_bck_cfg |

BlueTooth BCK Config |

0x9C001F90 |

G63.4 |

bt_sync_cfg |

BlueTooth SYNC Config |

0x9C001F94 |

G63.5 |

IFX0_SAMPLING_RATE_CNT |

IFX0_SAMPLING_RATE_CNT |

0x9C001F98 |

G63.6 |

IFX1_SAMPLING_RATE_CNT |

IFX1_SAMPLING_RATE_CNT |

0x9C001F9C |

G63.7 |

ASRC_CTRL |

ASRC_CTRL |

0x9C001FA0 |

G63.8 |

G63ADDR8_reserved |

Reserved |

0x9C001FA4 |

G63.9 |

G63ADDR9_reserved |

Reserved |

0x9C001FA8 |

G63.10 |

G63ADDR10_reserved |

Reserved |

0x9C001FAC |

G63.11 |

G63ADDR11_reserved |

Reserved |

0x9C001FB0 |

G63.12 |

G63ADDR12_reserved |

Reserved |

0x9C001FB4 |

G63.13 |

pgag_sample_cnt_0l |

ADAC_PGA_GAIN ctrl monitor sample counter (debug use.) |

0x9C001FB8 |

G63.14 |

ADAC_PGA_GAIN_0L_CTRL |

ADAC_PGA_GAIN_0L_CTRL |

0x9C001FBC |

G63.15 |

ADAC_PGA_GAIN_0R_CTRL |

ADAC_PGA_GAIN_0R_CTRL |

0x9C001FC0 |

G63.16 |

ADAC_PGA_GAIN_1L_CTRL |

ADAC_PGA_GAIN_1L_CTRL |

0x9C001FC4 |

G63.17 |

ADAC_PGA_GAIN_1R_CTRL |

ADAC_PGA_GAIN_1R_CTRL |

0x9C001FC8 |

G63.18 |

ADAC_PGA_GAIN_2R_CTRL |

ADAC_PGA_GAIN_2R_CTRL |

0x9C001FCC |

G63.19 |

AUD_AADC_AGC_STATUS |

DAGC0/1/2 STATUS |

0x9C001FD0 |

G63.20 |

AUD_AADC_AGC2_CFG0 |

DAGC2 config0 |

0x9C001FD4 |

G63.21 |

AUD_AADC_AGC2_CFG1 |

DAGC2 config1 |

0x9C001FD8 |

G63.22 |

AUD_AADC_AGC2_CFG2 |

DAGC2 config2 |

0x9C001FDC |

G63.23 |

AUD_AADC_AGC2_CFG3 |

DAGC2 config3 |

0x9C001FE0 |

G63.24 |

AUD_OPT_TEST_PAT |

AUD_OPT_TEST_PAT |

0x9C001FE4 |

G63.25 |

DSP_OPT_LSB |

DSP_OPT_LSB |

0x9C001FE8 |

G63.26 |

DSP_OPT_MSB |

DSP_OPT_MSB |

0x9C001FEC |

G63.27 |

int_adc_ctrl1 |

Internal ADC Config1 |

0x9C001FF0 |

G63.28 |

other_status |

aud other status |

0x9C001FF4 |

G63.29 |

CDRPLL_LOSD_CTRL |

CDRPLL_LOSD_CTRL |

0x9C001FF8 |

G63.30 |

LOSD_RELEASE_CNT |

LOSD_RELEASE_CNT |

0x9C001FFC |

G63.31 |

other_ctrl |

aud other ctrl |

Address |

Group No |

Register Name |

Description |

0x9C002000 |

G64.0 |

aud_a0_base |

Base Address |

0x9C002004 |

G64.1 |

aud_a0_length |

FIFO Length |

0x9C002008 |

G64.2 |

aud_a0_ptr |

FIFO Pointer |

0x9C00200C |

G64.3 |

aud_a0_cnt |

FIFO Count |

0x9C002010 |

G64.4 |

aud_a1_base |

Base Address |

0x9C002014 |

G64.5 |

aud_a1_length |

FIFO Length |

0x9C002018 |

G64.6 |

aud_a1_ptr |

FIFO Pointer |

0x9C00201C |

G64.7 |

aud_a1_cnt |

FIFO Count |

0x9C002020 |

G64.8 |

aud_a2_base |

Base Address |

0x9C002024 |

G64.9 |

aud_a2_length |

FIFO Length |

0x9C002028 |

G64.10 |

aud_a2_ptr |

FIFO Pointer |

0x9C00202C |

G64.11 |

aud_a2_cnt |

FIFO Count |

0x9C002030 |

G64.12 |

aud_a3_base |

Base Address |

0x9C002034 |

G64.13 |

aud_a3_length |

FIFO Length |

0x9C002038 |

G64.14 |

aud_a3_ptr |

FIFO Pointer |

0x9C00203C |

G64.15 |

aud_a3_cnt |

FIFO Count |

0x9C002040 |

G64.16 |

aud_a4_base |

Base Address |

0x9C002044 |

G64.17 |

aud_a4_length |

FIFO Length |

0x9C002048 |

G64.18 |

aud_a4_ptr |

FIFO Pointer |

0x9C00204C |

G64.19 |

aud_a4_cnt |

FIFO Count |

0x9C002050 |

G64.20 |

aud_a5_base |

Base Address |

0x9C002054 |

G64.21 |

aud_a5_length |

FIFO Length |

0x9C002058 |

G64.22 |

aud_a5_ptr |

FIFO Pointer |

0x9C00205C |

G64.23 |

aud_a5_cnt |

FIFO Count |

0x9C002060 |

G64.24 |

aud_a6_base |

Base Address |

0x9C002064 |

G64.25 |

aud_a6_length |

FIFO Length |

0x9C002068 |

G64.26 |

aud_a6_ptr |

FIFO Pointer |

0x9C00206C |

G64.27 |

aud_a6_cnt |

FIFO Count |

0x9C002070 |

G64.28 |

aud_a7_base |

Base Address |

0x9C002074 |

G64.29 |

aud_a7_length |

FIFO Length |

0x9C002078 |

G64.30 |

aud_a7_ptr |

FIFO Pointer |

0x9C00207C |

G64.31 |

aud_a7_cnt |

FIFO Count |

Address |

Group No |

Register Name |

Description |

0x9C002080 |

G65.0 |

aud_a8_base |

Base Address |

0x9C002084 |

G65.1 |

aud_a8_length |

FIFO Length |

0x9C002088 |

G65.2 |

aud_a8_ptr |

FIFO Pointer |

0x9C00208C |

G65.3 |

aud_a8_cnt |

FIFO Count |

0x9C002090 |

G65.4 |

aud_a9_base |

Base Address |

0x9C002094 |

G65.5 |

aud_a9_length |

FIFO Length |

0x9C002098 |

G65.6 |

aud_a9_ptr |

FIFO Pointer |

0x9C00209C |

G65.7 |

aud_a9_cnt |

FIFO Count |

0x9C0020A0 |

G65.8 |

aud_a10_base |

Base Address |

0x9C0020A4 |

G65.9 |

aud_a10_length |

FIFO Length |

0x9C0020A8 |

G65.10 |

aud_a10_ptr |

FIFO Pointer |

0x9C0020AC |

G65.11 |

aud_a10_cnt |

FIFO Count |

0x9C0020B0 |

G65.12 |

aud_a11_base |

Base Address |

0x9C0020B4 |

G65.13 |

aud_a11_length |

FIFO Length |

0x9C0020B8 |

G65.14 |

aud_a11_ptr |

FIFO Pointer |

0x9C0020BC |

G65.15 |

aud_a11_cnt |

FIFO Count |

0x9C0020C0 |

G65.16 |

aud_a12_base |

Base Address |

0x9C0020C4 |

G65.17 |

aud_a12_length |

FIFO Length |

0x9C0020C8 |

G65.18 |

aud_a12_ptr |

FIFO Pointer |

0x9C0020CC |

G65.19 |

aud_a12_cnt |

FIFO Count |

0x9C0020D0 |

G65.20 |

aud_a13_base |

Base Address |

0x9C0020D4 |

G65.21 |

aud_a13_length |

FIFO Length |

0x9C0020D8 |

G65.22 |

aud_a13_ptr |

FIFO Pointer |

0x9C0020DC |

G65.23 |

aud_a13_cnt |

FIFO Count |

0x9C0020E0 |

G65.24 |

aud_a14_base |

Base Address |

0x9C0020E4 |

G65.25 |

aud_a14_length |

FIFO Length |

0x9C0020E8 |

G65.26 |

aud_a14_ptr |

FIFO Pointer |

0x9C0020EC |

G65.27 |

aud_a14_cnt |

FIFO Count |

0x9C0020F0 |

G65.28 |

aud_a15_base |

Base Address |

0x9C0020F4 |

G65.29 |

aud_a15_length |

FIFO Length |

0x9C0020F8 |

G65.30 |

aud_a15_ptr |

FIFO Pointer |

0x9C0020FC |

G65.31 |

aud_a15_cnt |

FIFO Count |

Address |

Group No |

Register Name |

Description |

0x9C002100 |

G66.0 |

aud_a16_base |

Base Address |

0x9C002104 |

G66.1 |

aud_a16_length |

FIFO Length |

0x9C002108 |

G66.2 |

aud_a16_ptr |

FIFO Pointer |

0x9C00210C |

G66.3 |

aud_a16_cnt |

FIFO Count |

0x9C002110 |

G66.4 |

aud_a17_base |

Base Address |

0x9C002114 |

G66.5 |

aud_a17_length |

FIFO Length |

0x9C002118 |

G66.6 |

aud_a17_ptr |

FIFO Pointer |

0x9C00211C |

G66.7 |

aud_a17_cnt |

FIFO Count |

0x9C002120 |

G66.8 |

aud_a18_base |

Base Address |

0x9C002124 |

G66.9 |

aud_a18_length |

FIFO Length |

0x9C002128 |

G66.10 |

aud_a18_ptr |

FIFO Pointer |

0x9C00212C |

G66.11 |

aud_a18_cnt |

FIFO Count |

0x9C002130 |

G66.12 |

aud_a19_base |

Base Address |

0x9C002134 |

G66.13 |

aud_a19_length |

FIFO Length |

0x9C002138 |

G66.14 |

aud_a19_ptr |

FIFO Pointer |

0x9C00213C |

G66.15 |

aud_a19_cnt |

FIFO Count |

0x9C002140 |

G66.16 |

aud_a20_base |

Base Address |

0x9C002144 |

G66.17 |

aud_a20_length |

FIFO Length |

0x9C002148 |

G66.18 |

aud_a20_ptr |

FIFO Pointer |

0x9C00214C |

G66.19 |

aud_a20_cnt |

FIFO Count |

0x9C002150 |

G66.20 |

aud_a21_base |

Base Address |

0x9C002154 |

G66.21 |

aud_a21_length |

FIFO Length |

0x9C002158 |

G66.22 |

aud_a21_ptr |

FIFO Pointer |

0x9C00215C |

G66.23 |

aud_a21_cnt |

FIFO Count |

0x9C002160 |

G66.24 |

aud_a22_base |

Base Address |

0x9C002164 |

G66.25 |

aud_a22_length |

FIFO Length |

0x9C002168 |

G66.26 |

aud_a22_ptr |

FIFO Pointer |

0x9C00216C |

G66.27 |

aud_a22_cnt |

FIFO Count |

0x9C002170 |

G66.28 |

aud_a23_base |

Base Address |

0x9C002174 |

G66.29 |

aud_a23_length |

FIFO Length |

0x9C002178 |

G66.30 |

aud_a23_ptr |

FIFO Pointer |

0x9C00217C |

G66.31 |

aud_a23_cnt |

FIFO Count |

Address |

Group No |

Name |

Description |

0x9C002180 |

G67.0 |

aud_grm_master_gain |

Gain Control |

0x9C002184 |

G67.1 |

aud_grm_gain_control_0 |

Gain Control |

0x9C002188 |

G67.2 |

aud_grm_gain_control_1 |

Gain Control |

0x9C00218C |

G67.3 |

aud_grm_gain_control_2 |

Gain Control |

0x9C002190 |

G67.4 |

aud_grm_gain_control_3 |

Gain Control |

0x9C002194 |

G67.5 |

aud_grm_gain_control_4 |

Gain Control |

0x9C002198 |

G67.6 |

aud_grm_mix_control_0 |

Mixer Setting |

0x9C00219C |

G67.7 |

aud_grm_mix_control_1 |

Mixer Setting |

0x9C0021A0 |

G67.8 |

aud_grm_mix_control_2 |

Mixer Setting |

0x9C0021A4 |

G67.9 |

aud_grm_switch_0 |

Channel Switch |

0x9C0021A8 |

G67.10 |

aud_grm_switch_1 |

Channel Switch |

0x9C0021AC |

G67.11 |

aud_grm_switch_int |

INT DAC Channel Switch |

0x9C0021B0 |

G67.12 |

aud_grm_delta_volume |

Gain Update |

0x9C0021B4 |

G67.13 |

aud_grm_delta_ramp_pcm |

Gain Update |

0x9C0021B8 |

G67.14 |

aud_grm_delta_ramp_risc |

Gain Update |

0x9C0021BC |

G67.15 |

aud_grm_delta_ramp_linein |

Gain Update |

0x9C0021C0 |

G67.16 |

aud_grm_other |

Other Setting |

0x9C0021C4 |

G67.17 |

aud_grm_gain_control_5 |

Gain Control |

0x9C0021C8 |

G67.18 |

aud_grm_gain_control_6 |

Gain Control |

0x9C0021CC |

G67.19 |

aud_grm_gain_control_7 |

Gain Control |

0x9C0021D0 |

G67.20 |

aud_grm_gain_control_8 |

Gain Control |

0x9C0021D4 |

G67.21 |

aud_grm_fifo_eflag |

FIFO Error Flag |

0x9C0021D8 |

G67.22 |

aud_grm_gain_control_9 |

IEC Tx Interface Gain |

0x9C0021DC |

G67.23 |

aud_grm_gain_control_10 |

I2S Tx Interface Gain |

0x9C0021E0 |

G67.24 |

aud_grm_switch_hdmi |

HDMI DAC Channel Switch |

0x9C0021E4 |

G67.25 |

aud_grm_gain_control_11 |

New Gain Control |

0x9C0021E8 |

G67.26 |

reserved |

Reserved |

0x9C0021EC |

G67.27 |

reserved |

Reserved |

0x9C0021F0 |

G67.28 |

reserved |

Reserved |

0x9C0021F4 |

G67.29 |

reserved |

Reserved |

0x9C0021F8 |

G67.30 |

reserved |

Reserved |

0x9C0021FC |

G67.31 |

reserved |

Reserved |

Address |

Group No |

Register Name |

Description |

0x9C002200 |

G68.0 |

Reserved |

Reserved |

0x9C002204 |

G68.1 |

Reserved |

Reserved |

0x9C002208 |

G68.2 |

Reserved |

Reserved |

0x9C00220C |

G68.3 |

Reserved |

Reserved |

0x9C002210 |

G68.4 |

Reserved |

Reserved |

0x9C002214 |

G68.5 |

Reserved |

Reserved |

0x9C002218 |

G68.6 |

Reserved |

Reserved |

0x9C00221C |

G68.7 |

Reserved |

Reserved |

0x9C002220 |

G68.8 |

Reserved |

Reserved |

0x9C002224 |

G68.9 |

Reserved |

Reserved |

0x9C002228 |

G68.10 |

Reserved |

Reserved |

0x9C00222C |

G68.11 |

Reserved |

Reserved |

0x9C002230 |

G68.12 |

Reserved |

Reserved |

0x9C002234 |

G68.13 |

Reserved |

Reserved |

0x9C002238 |

G68.14 |

Reserved |

Reserved |

0x9C00223C |

G68.15 |

Reserved |

Reserved |

0x9C002240 |

G68.16 |

Reserved |

Reserved |

0x9C002244 |

G68.17 |

Reserved |

Reserved |

0x9C002248 |

G68.18 |

Reserved |

Reserved |

0x9C00224C |

G68.19 |

Reserved |

Reserved |

0x9C002250 |

G68.20 |

Reserved |

Reserved |

0x9C002254 |

G68.21 |

Reserved |

Reserved |

0x9C002258 |

G68.22 |

Reserved |

Reserved |

0x9C00225C |

G68.23 |

Reserved |

Reserved |

0x9C002260 |

G68.24 |

AUD_MONITOR_TRIGGER |

AUD_MONITOR |

0x9C002264 |

G68.25 |

AUD_SBAR_CNT |

AUD_SBAR_CNT |

0x9C002268 |

G68.26 |

AUD_SBAR_CYCLE |

AUD_SBAR_CYCLE |

0x9C00226C |

G68.27 |

AUD_MAX_SBAR_CYCLE |

AUD_MAX_SBAR_CYCLE |

0x9C002270 |

G68.28 |

AUD_MIN_SBAR_CYCLE |

AUD_MIN_SBAR_CYCLE |

0x9C002274 |

G68.29 |

AUD_SBAR_STATUS |

AUD_SBAR_STATUS |

0x9C002278 |

G68.30 |

Reserved |

Reserved |

0x9C00227C |

G68.31 |

Reserved |

Reserved |

Address |

Group No |

Register Name |

Description |

0x9C002280 |

G69.0 |

adcp_gps_ch_enable |

ADCPRC GPS Configuration Group 1 |

0x9C002284 |

G69.1 |

adcp_gps_fubypass |

ADCPRC GPS Configuration Group 2 |

0x9C002288 |

G69.2 |

adcp_gps_mode_ctrl |

ADCPRC GPS Mode Control |

0x9C00228C |

G69.3 |

adcp_gps_init_ctrl |

ADCP GPS Initialization Control |

0x9C002290 |

G69.4 |

adcp_gps_coeff_din |

Coefficient Data Input |

0x9C002294 |

G69.5 |

adcp_gps_agc_cfg |

ADCPRC GPS AGC Configuration of Ch0/1 |

0x9C002298 |

G69.6 |

adcp_gps_agc_cfg2 |

ADCPRC GPS AGC Configuration of Ch2/3 |

0x9C00229C |

G69.7 |

adcp_gps_gain_0 |

ADCPRC GPS System Gain0 |

0x9C0022A0 |

G69.8 |

adcp_gps_gain_1 |

ADCP GPS System Gain1 |

0x9C0022A4 |

G69.9 |

adcp_gps_gain_2 |

ADCP GPS System Gain2 |

0x9C0022A8 |

G69.10 |

adcp_gps_gain_3 |

ADCP GPS System Gain3 |

0x9C0022AC |

G69.11 |

adcp_gps_risc_gain |

ADCP GPS RISC Gain |

0x9C0022B0 |

G69.12 |

adcp_gps_mic_l |

ADCPRC GPS Microphone - in Left Channel Data |

0x9C0022B4 |

G69.13 |

adcp_gps_mic_r |

ADCPRC GPS Microphone - in Right Channel Data |

0x9C0022B8 |

G69.14 |

adcp_gps_agc_gain |

ADCPRC GPS AGC Gain |

0x9C0022BC |

G69.15 |

i2s_pwm_control_1 |

Reserved |

0x9C0022C0 |

G69.16 |

i2s_pwm_control_2 |

Reserved |

0x9C0022C4 |

G69.17 |

i2s_pwm_control_3 |

Reserved |

0x9C0022C8 |

G69.18 |

i2s_pwm_control_4 |

Reserved |

0x9C0022CC |

G69.19 |

classd_mos_control |

Reserved |

0x9C0022D0 |

G69.20 |

G69ADDR20_reserved0 |

Reserved |

0x9C0022D4 |

G69.21 |

G69ADDR21_reserved0 |

Reserved |

0x9C0022D8 |

G69.22 |

G69ADDR22_reserved0 |

Reserved |

0x9C0022DC |

G69.23 |

G69ADDR23_reserved0 |

Reserved |

0x9C0022E0 |

G69.24 |

G69ADDR24_reserved0 |

Reserved |

0x9C0022E4 |

G69.25 |

G69ADDR25_reserved0 |

Reserved |

0x9C0022E8 |

G69.26 |

G69ADDR26_reserved0 |

Reserved |

0x9C0022EC |

G69.27 |

G69ADDR27_reserved0 |

Reserved |

0x9C0022F0 |

G69.28 |

G69ADDR28_reserved0 |

Reserved |

0x9C0022F4 |

G69.29 |

G69ADDR29_reserved0 |

Reserved |

0x9C0022F8 |

G69.30 |

G69ADDR30_reserved0 |

Reserved |

0x9C0022FC |

G69.31 |

G69ADDR31_reserved0 |

Reserved |

Address |

Group No |

Register Name |

Description |

0x9C002300 |

G70.0 |

fifo_near_value_0_1 |

AUD FIFO NEAR VALUE 0/1 |

0x9C002304 |

G70.1 |

fifo_near_value_2_3 |

AUD FIFO NEAR VALUE 2/3 |

0x9C002308 |

G70.2 |

fifo_near_value_4_5 |

AUD FIFO NEAR VALUE 4/5 |

0x9C00230C |

G70.3 |

fifo_near_value_6_7 |

AUD FIFO NEAR VALUE 6/7 |

0x9C002310 |

G70.4 |

fifo_near_value_8_9 |

AUD FIFO NEAR VALUE 8/9 |

0x9C002314 |

G70.5 |

fifo_near_value_10_11 |

AUD FIFO NEAR VALUE 10/11 |

0x9C002318 |

G70.6 |

fifo_near_value_12_13 |

AUD FIFO NEAR VALUE 12/13 |

0x9C00231C |

G70.7 |

fifo_near_value_14_15 |

AUD FIFO NEAR VALUE 14/15 |

0x9C002320 |

G70.8 |

fifo_near_status |

AUD FIFO NEAR STATUS |

0x9C002324 |

G70.9 |

fifo_status |

AUD FIFO STATUS |

0x9C002328 |

G70.10 |

fifo_near_mask |

AUD FIFO NEAR STATUS MASK |

0x9C00232C |

G70.11 |

fifo_status_mask |

AUD FIFO STATUS MASK |

0x9C002330 |

G70.12 |

G70ADDR20_reserved0 |

Reserved |

0x9C002334 |

G70.13 |

G70ADDR21_reserved0 |

Reserved |

0x9C002338 |

G70.14 |

fifo_near_value_16_17 |

AUD FIFO NEAR VALUE 16/17 |

0x9C00233C |

G70.15 |

fifo_near_value_18_19 |

AUD FIFO NEAR VALUE 18/19 |

0x9C002340 |

G70.16 |

fifo_near_value_20_21 |

AUD FIFO NEAR VALUE 20/21 |

0x9C002344 |

G70.17 |

fifo_near_value_22_23 |

AUD FIFO NEAR VALUE 22/23 |

0x9C002348 |

G70.18 |

fifo_near_value_24_25 |

AUD FIFO NEAR VALUE 24/25 |

0x9C00234C |

G70.19 |

fifo_near_value_26_27 |

AUD FIFO NEAR VALUE 26/27 |

0x9C002350 |

G70.20 |

G70ADDR20_reserved0 |

Reserved |

0x9C002354 |

G70.21 |

G70ADDR21_reserved0 |

Reserved |

0x9C002358 |

G70.22 |

G70ADDR22_reserved0 |

Reserved |

0x9C00235C |

G70.23 |

G70ADDR23_reserved0 |

Reserved |

0x9C002360 |

G70.24 |

G70ADDR24_reserved0 |

Reserved |

0x9C002364 |

G70.25 |

G70ADDR25_reserved0 |

Reserved |

0x9C002368 |

G70.26 |

G70ADDR26_reserved0 |

Reserved |

0x9C00236C |

G70.27 |

G70ADDR27_reserved0 |

Reserved |

0x9C002370 |

G70.28 |

G70ADDR28_reserved0 |

Reserved |

0x9C002374 |

G70.29 |

G70ADDR29_reserved0 |

Reserved |

0x9C002378 |

G70.30 |

G70ADDR30_reserved0 |

Reserved |

0x9C00237C |

G70.31 |

G70ADDR31_reserved0 |

Reserved |

Address |

Group No |

Register Name |

Description |

0x9C002380 |

G71.0 |

aud_a24_base |

Base Address |

0x9C002384 |

G71.1 |

aud_a24_length |

FIFO Length |

0x9C002388 |

G71.2 |

aud_a24_ptr |

FIFO Pointer |

0x9C00238C |

G71.3 |

aud_a24_cnt |

FIFO Count |

0x9C002390 |

G71.4 |

aud_a25_base |

Base Address |

0x9C002394 |

G71.5 |

aud_a25_length |

FIFO Length |

0x9C002398 |

G71.6 |

aud_a25_ptr |

FIFO Pointer |

0x9C00239C |

G71.7 |

aud_a25_cnt |

FIFO Count |

0x9C0023A0 |

G71.8 |

aud_a26_base |

Base Address |

0x9C0023A4 |

G71.9 |

aud_a26_length |

FIFO Length |

0x9C0023A8 |

G71.10 |

aud_a26_ptr |

FIFO Pointer |

0x9C0023AC |

G71.11 |

aud_a26_cnt |

FIFO Count |

0x9C0023B0 |

G71.12 |

aud_a27_base |

Base Address |

0x9C0023B4 |

G71.13 |

aud_a27_length |

FIFO Length |

0x9C0023B8 |

G71.14 |

aud_a27_ptr |

FIFO Pointer |

0x9C0023BC |

G71.15 |

aud_a27_cnt |

FIFO Count |

0x9C0023C0 |

G71.16 |

aud_a28_base |

Base Address |

0x9C0023C4 |

G71.17 |

aud_a28_length |

FIFO Length |

0x9C0023C8 |

G71.18 |

aud_a28_ptr |

FIFO Pointer |

0x9C0023CC |

G71.19 |

aud_a28_cnt |

FIFO Count |

0x9C0023D0 |

G71.20 |

aud_a29_base |

Base Address |

0x9C0023D4 |

G71.21 |

aud_a29_length |

FIFO Length |

0x9C0023D8 |

G71.22 |

aud_a29_ptr |

FIFO Pointer |

0x9C0023DC |

G71.23 |

aud_a29_cnt |

FIFO Count |

0x9C0023E0 |

G71.24 |

G71ADDR24_reserved0 |

Reserved |

0x9C0023E4 |

G71.25 |

G71ADDR25_reserved0 |

Reserved |

0x9C0023E8 |

G71.26 |

G71ADDR26_reserved0 |

Reserved |

0x9C0023EC |

G71.27 |

G71ADDR27_reserved0 |

Reserved |

0x9C0023F0 |

G71.28 |

G71ADDR28_reserved0 |

Reserved |

0x9C0023F4 |

G71.29 |

G71ADDR29_reserved0 |

Reserved |

0x9C0023F8 |

G71.30 |

G71ADDR30_reserved0 |

Reserved |

0x9C0023FC |

G71.31 |

G71ADDR31_reserved0 |

Reserved |

Address |

Group No |

Register Name |

Description |

0x9C002400 |

G72.0 |

tdm_rx_cfg0 |

TDM RX CONFIG 0 |

0x9C002404 |

G72.1 |

tdm_rx_cfg1 |

TDM RX CONFIG 1 |

0x9C002408 |

G72.2 |

tdm_rx_cfg2 |

TDM RX CONFIG 2 |

0x9C00240C |

G72.3 |

tdm_rx_cfg3 |

TDM RX CONFIG 3 |

0x9C002410 |

G72.4 |

G72ADDR4_reserved0 |

Reserved |

0x9C002414 |

G72.5 |

G72ADDR5_reserved0 |

Reserved |

0x9C002418 |

G72.6 |

tdm_tx_cfg0 |

TDM TX CONFIG 0 |

0x9C00241C |

G72.7 |

tdm_tx_cfg1 |

TDM TX CONFIG 1 |

0x9C002420 |

G72.8 |

tdm_tx_cfg2 |

TDM TX CONFIG 2 |

0x9C002424 |

G72.9 |

tdm_tx_cfg3 |

TDM TX CONFIG 3 |

0x9C002428 |

G72.10 |

tdm_tx_cfg4 |

TDM TX CONFIG 4 |

0x9C00242C |

G72.11 |

G72ADDR11_reserved0 |

Reserved |

0x9C002430 |

G72.12 |

G72ADDR12_reserved0 |

Reserved |

0x9C002434 |

G72.13 |

G72ADDR13_reserved0 |

Reserved |

0x9C002438 |

G72.14 |

pdm_cfg0 |

PDM CONFIG 0 |

0x9C00243C |

G72.15 |

pdm_cfg1 |

PDM CONFIG 1 |

0x9C002440 |

G72.16 |

pdm_cfg2 |

PDM CONFIG 2 |

0x9C002444 |

G72.17 |

pdm_cfg3 |

PDM CONFIG 3 |

0x9C002448 |

G72.18 |

pdm_cfg4 |

PDM CONFIG 4 |

0x9C00244C |

G72.19 |

pdm_cfg5 |

PDM CONFIG 5 |

0x9C002450 |

G72.20 |

G72ADDR26_reserved0 |

Reserved |

0x9C002454 |

G72.21 |

G72ADDR27_reserved0 |

Reserved |

0x9C002458 |

G72.22 |

aud_tdmtx_xck_cfg |

TDM XCK Configuration |

0x9C00245C |

G72.23 |

aud_tdmtx_bck_cfg |

TDM BCK Configuration |

0x9C002460 |

G72.24 |

aud_tdmrx_xck_cfg |

TDM XCK Configuration |

0x9C002464 |

G72.25 |

aud_tdmrx_bck_cfg |

TDM BCK Configuration |

0x9C002468 |

G72.26 |

aud_pdmrx_bck_cfg |

PDM XCK Configuration |

0x9C00246C |

G72.27 |

aud_pdmrx_xck_cfg |

PDM BCK Configuration |

0x9C002470 |

G72.28 |

G72ADDR28_reserved0 |

Reserved |

0x9C002474 |

G72.29 |

G72ADDR29_reserved0 |

Reserved |

0x9C002478 |

G72.30 |

tdm_pdm_tx_sel |

TDM or PDM TX selection |

0x9C00247C |

G72.31 |

G72ADDR31_reserved0 |

Reserved |

Registers Description

Audio

PChip Group 60AUD REG G0

AUD Group 0 Registers.

60.0AUD Interface Control (audif ctrl)

Address:0x9C001E00

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A0 reserved131:18RO RESERVED

Reserved for further usage. CONFIG BT BCK STOP17 RW BCK Clock Enable

Active high to disable the BCK output of audio hardware

set 0.

CONFIG BT LRCK STOP16 RW LRCK Clock Enable

Active high to disable the LRCK output of audio hardware set 0.

AUDIO OFFSET15:13 RW Audio Offect Setting

Reserved for further usage. CONFIG1 BCK STOP12 RW BCK Clock Enable

Active high to disable the BCK output of audio hardware

set 1.

CONFIG1 LRCK STOP11 RW LRCK Clock Enable

Active high to disable the LRCK output of audio hardware set 1.

603

CONFIG0 BCK STOP |

10 |

RW |

BCK Clock Enable |

CONFIG0 LRCK STOP |

9 |

RW |

LRCK Clock Enable |

ADCP GPS RST B |

8 |

RW |

ADCPRC GPS Reset |

ADCP RST B |

7 |

RW |

ADCPRC Reset |

IEC1 TX RST |

6 |

RW |

S/PDIF Transmitter Reset |

INT ADC RST B |

5 |

RW |

Internal ADC Configuration Reset |

EXT ADC RST B |

4 |

RW |

External ADC Configuration Reset |

IEC0 TX RST |

3 |

RW |

S/PDIF Transmitter Reset |

PCM RST B |

2 |

RW |

Audio PCM Reset |

G60A0 reserved0 |

1 |

RW |

RESERVED |

FIFO RST B |

0 |

RW |

Audio FIFO Reset |

60.1Audio FIFO Request Enable (aud enable)

Address:0x9C001E04

Reset: 0x005F 0000

Field NameBitAccessDescription

G60A1 reserved331:23RO RESERVED

Reserved for further usage.

PCM ENABLE UNLINK |

22 |

RW |

PCM FIFO Unlinked Enable |

I2S PWM ENABLE |

21 |

RW |

I2S PWM Enable |

PCM ENABLE UNLINK |

20:16 |

RW |

PCM FIFO Unlinked Enable |

G60A1 reserved2 |

15 |

RW |

RESERVED |

BT ENABLE |

14 |

RW |

BT TX(RX) FIFO Enable |

G60A1 reserved1 |

13 |

RW |

RESERVED |

TDM PDM IN ENABLE |

12 |

RW |

TDM or PDM FIFO Enable |

HDMI0 IN ENABLE |

11 |

RW |

HDMI RX FIFO Enable |

SPDIF2 IN ENABLE |

10 |

RW |

S/PDIF RX 2 FIFO Enable |

SPDIF1 IN ENABLE |

9 |

RW |

S/PDIF RX 1 FIFO Enable |

SPDIF1 OUT ENABLE |

8 |

RW |

S/PDIF TX 1 FIFO Enable |

RECORD ENABLE |

7 |

RW |

Record FIFO Enable |

SPDIF0 IN ENABLE |

6 |

RW |

S/PDIF RX 0 FIFO Enable |

INT ADC ENABLE |

5 |

RW |

Internal ADC FIFO Enable |

G60A1 reserved0 |

4 |

RW |

RESERVED |

EXT ADC ENABLE |

3 |

RW |

External ADC FIFO Enable |

RISC ENABLE |

2 |

RW |

RISC FIFO Enable |

SPDIF0 OUT ENABLE |

1 |

RW |

S/PDIF TX 0 FIFO Enable |

PCM ENABLE |

0 |

RW |

PCM FIFO Enable |

60.2Audio PCM (I2S) Format Configuration (pcm cfg)

Address:0x9C001E08

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A2 reserved031:10RO RESERVED

Reserved for further usage. PCM CFG LRSEL9:8 RW BCK and LRCK Selection

0x0: Master mode. (default)

Use CLKGENA EXT DAC BCK O as BCK and generated

CONFIG0 LRCK O as LRCK.

0x1: Master mode.

Use CLKGENA EXT ADC BCK O as BCK and generated

CONFIG1 LRCK O as LRCK.

0x2: Slave mode.

Use external PI AU BCK I as BCK and PI AU BCK I as

LRCK.

0x3: Slave mode.

Use external PI ADC BCK I as BCK and PI ADC BCK I as

LRCK.

I2S TX0 CFG EDGE7 RW Synchronized BCK Edge Selection

0: Serial data is valid on rising edge of BCK. (default)

1: Serial data is valid on falling edge of BCK.

I2S TX0 CFG LRCYCLE |

6:5 |

RW |

LRCK Cycle Selection |

I2S TX0 CFG PARITY |

4 |

RW |

PCM Data Parity |

I2S TX0 CFG DWIDE |

3:2 |

RW |

PCM Data Width |

I2S TX0 CFG JUSTIFY |

1 |

RW |

PCM Data Justify |

|

|

|

|

60.3Mute Flag of I2S TX Module (i2s mute flag ctrl)

Address: 0x9C001E0C Reset: 0x0000 0000

Field NameBitAccessDescription

G60A3 reserved231:15RO RESERVED

Reserved for further usage. I2S TX0 MUTE 14 RW I2S TX0 Mute Control

Active high to mute corresponding channel.

default are not mute. bit 0: Mute channel 6.

G60A3 reserved113 RW RESERVED

Reserved for further usage.

I2S TX0 MUTE |

12:8 |

RW |

I2S TX0 Mute Control |

G60A3 reserved1 |

7:6 |

RO |

RESERVED |

I2S TX1 MUTE FLAG |

5 |

RO |

Mute Flag for I2S TX1 |

I2S TX0 MUTE FLAG |

4 |

RO |

Mute Flag for I2S TX0 |

G60A3 reserved0 |

3 |

RO |

RESERVED |

MUTE THRESHOLD |

2:0 |

RW |

Mute Threshold |

60.4 External ADC (I2S) Format Configuration (ext adc cfg)

Address:0x9C001E10

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A4 reserved031:10RO RESERVED

|

|

|

Reseved.Replaced by I2S RX1 CFG LRSEL for EX- TADC HDMIRX SWAP |

I2S RX0 CFG EDGE |

7 |

RW |

Synchronized BCK Edge Selection |

I2S RX0 CFG LRCYCLE |

6:5 |

RW |

LRCK Cycle Selection |

Reserved for further usage. ADC CFG LRSEL9:8 RW BCK and LRCK Selection

I2S RX0 CFG PARITY |

4 |

RW |

PCM Data Parity |

I2S RX0 CFG DWIDE |

3:2 |

RW |

PCM Data Width |

I2S RX0 CFG JUSTIFY |

1 |

RW |

PCM Data Justify |

I2S RX0 CFG DELAY |

0 |

RW |

ext dac format configuration |

60.5Internal DAC Control 0 (ACODEC CFG0) (int dac ctrl0)

Address:0x9C001E14

Reset: 0xE018 8013

Field NameBitAccessDescription

aio da31:30 RW DAC GPIO Mode

0x0: DA0/1/2/3 are all gpio

0x1: DA1/2/3 are gpio (2ch DAC mode)

0x2: DA3 is gpio (5.1ch DAC mode)

0x3: No gpio (7.1ch DAC mode) (default)

en dither 29 RW Enable dither function

0: disable. (default)

1: enable

G60A5 reserved128 RW reserved

RCON127:26 RW DAC1 RCF frequence Response R-option

str225 RW Enable to enhance DAC OP driving power

0: disable. (default)

1: enable

str124 RW Enable to enhance DAC OP driving power

0: disable. (default)

1: enable

str0 |

23 |

RW |

Enable to enhance DAC OP driving power |

fs |

22:20 |

RW |

Sample Rate Control |

ckinv |

19 |

RW |

DACLK inversion |

dwa sel |

18 |

RW |

Enable data weighting average function to reduce noise |

enzcd2 |

17 |

RW |

Enable zero crossover detection function |

enzcd1 |

16 |

RW |

Enable zero crossover detection function |

enzcd0 |

15 |

RW |

Enable zero crossover detection function |

aen |

14:12 |

RW |

Auto-sleep Enable |

en ref |

11 |

RW |

Common mode voltage reference enable |

den |

10:8 |

RW |

De-emphasis Enable |

RCON0 |

7:6 |

RW |

DAC0 RCF frequence Response R-option |

|

|

|

|

|

|

|

|

pwdal1 |

3 |

RW |

Left channel power down |

pwdar1 |

2 |

RW |

Right channel power down |

pwdal0 |

1 |

RW |

Left channel power down |

pwdar0 0 RW Right channel power down

Active high to enter power-down mode. (default)

60.6Internal ADC Config 0 (int adc ctrl0)

Address:0x9C001E18

Reset: 0x8000 0726

Field NameBitAccessDescription

rstb 31 RW ACODEC Reset

This reset bit is applied to ADC. Active low to enter power- down mode. (default)

AADC ENZCD1 30 RW ENZCD

ADC 1 Zero crossover detection function control

0: Function enable

1: Funcition disable (default)

G60A6 reserved429 RW

pdvref1 28 RW ADC 1 Enable reference voltage "VREF" power-down

Active high for enable

pdadl1 27 RW ADC 1 Power Down L Channel

Active high to power-down pdadr1 26 RW ADC 1 Power Down R Channel

Active high to power-down

enhpl125 RW ADC 1 Enable HPF of L Channel

Active high for enable

enhpr124 RW ADC 1 Enable HPF of R Channel

Active high for enable ovrs123:22 RW ADC 1 Oversample Range

Select ADC input limit range.

0x0: 0.84*Full range (default)

0x1: 0.71*Full range

0x2: 0.60*Full range

0x3: 0.50*Full range

G60A6 reserved321 RW reserved

gsel1 l |

20:16 |

RW |

ADC 1 L-channel Gain Control |

G60A6 reserved2 |

15 |

RW |

reserved |

|

|

|

|

|

|

|

|

|

|

|

|

pdadl0 |

11 |

RW |

ADC 0 Power Down L Channel |

pdadr0 |

10 |

RW |

ADC 0 Power Down R Channel |

enhpl0 |

9 |

RW |

ADC 0 Enable HPF of L Channel |

enhpr0 |

8 |

RW |

ADC 0 Enable HPF of R Channel |

ovrs0 |

7:6 |

RW |

ADC 0 Oversample Range |

G60A6 reserved0 |

5 |

RW |

reserved |

4:0 |

RW |

ADC 0 L-channel Gain Control |

|

|

Range of gain is 6dB downto -24 dB. Step size is 1dB. 0x1f |

|

|

is mute. |

|

|

0x00: 6dB |

|

|

0x01: 5dB |

|

|

... |

|

|

0x1e: -24dB (default) |

|

|

0x1f: mute |

gsel0 l

60.7ADC Input Path Switch (adc in path switch)

Address: 0x9C001E1C Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

G60A7 reserved0 |

31:2 |

RO |

RESERVED |

FPGA MODE |

1 |

RW |

Input Source Selection of Channel 0/1 |

ADC SWITCH |

0 |

RW |

ADC Switch |

60.8Internal ADC and DAC (I2S) Format Configuration (int adc dac cfg)

Address:0x9C001E20

Reset: 0x0010 004D

Field Name |

BitAccess |

Description |

G60A8 reserved3 |

31:26RO |

RESERVED |

G60A8 reserved2 |

25:24 RW |

RESERVED |

INT ADC CFG EDGE |

23 |

RW |

Synchronized BCK Edge Selection |

INT ADC CFG LRCYCLE |

22:21 |

RW |

LRCK Cycle Selection |

INT ADC CFG PARITY |

20 |

RW |

PCM Data Parity |

INT ADC CFG DWIDE |

19:18 |

RW |

PCM Data Width |

INT ADC CFG JUSTIFY |

17 |

RW |

PCM Data Justify |

INT ADC CFG DELAY |

16 |

RW |

ext dac format configuration |

G60A8 reserved1 |

15:10 |

RO |

RESERVED |

G60A8 reserved0 |

9:8 |

RW |

RESERVED |

INT DAC CFG EDGE |

7 |

RW |

Synchronized BCK Edge Selection |

INT DAC CFG LRCYCLE |

6:5 |

RW |

LRCK Cycle Selection |

INT DAC CFG PARITY |

4 |

RW |

PCM Data Parity |

INT DAC CFG DWIDE |

3:2 |

RW |

PCM Data Width |

INT DAC CFG JUSTIFY |

1 |

RW |

PCM Data Justify |

INT DAC CFG DELAY |

0 |

RW |

ext dac format configuration |

60.9 Reserved (G60ADDR9 reserved)

Address:0x9C001E24

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A9 reserved031:0RO reserved

60.10S/PDIF Configuration (iec cfg)

Address:0x9C001E28

Reset: 0x0000 4000

Field NameBitAccessDescription

G60A10 reserved031:18RO RESERVED

Reserved for further usage. IEC0 RX NEW MODE 17 RW IEC0 RX New Mode Enable

Active high to enable IEC0 RX New Mode.

IEC1 RX SOURCE SEL16 RW Input Source Selection of S/PDIF RX1

Both PI IEC1 RX and HDMI ARC SPDIF TX input ports can be the input source of S/PDIF RX1.

0: Select PI IEC1 RX (default)

1: Select HDMI ARC SPDIF TX

IEC0 RX SOURCE SEL |

15 |

RW |

Input Source Selection of S/PDIF RX0 |

IEC AGENT ENABLE |

14 |

RW |

IEC Agent Enable |

IEC2 RX CHANNEL SEL |

13 |

RW |

Channel Selection of S/PDIF RX2 for upadting channel status |

IEC2 RX LR ATTRIBUTE |

12 |

RW |

Show the Channel Flag of S/PDIF RX2 |

IEC1 RX CHANNEL SEL |

11 |

RW |

Channel Selection of S/PDIF RX1 for upadting channel status |

IEC1 RX LR ATTRIBUTE |

10 |

RW |

Show the Channel Flag of S/PDIF RX1 |

IEC0 RX CHANNEL SEL |

9 |

RW |

Channel Selection of S/PDIF RX0 for upadting channel status |

IEC0 RX LR ATTRIBUTE |

8 |

RW |

Show the Channel Flag of S/PDIF RX0 |

IEC1 TX MUTE |

7 |

RW |

Mute S/PDIF TX1 Source Data |

IEC1 TX RAW |

6 |

RW |

S/PDIF TX1 Ramp Function Bypass |

IEC1 TX CSS MODE |

5 |

RW |

CSS Mode of S/PDIF TX1 |

IEC1 TX FREEZE |

4 |

RW |

Freeze S/PDIF TX1 Output Port |

IEC0 TX MUTE |

3 |

RW |

Mute S/PDIF TX0 Source Data |

IEC0 TX RAW |

2 |

RW |

S/PDIF TX0 Ramp Function Bypass |

IEC0 TX CSS MODE |

1 |

RW |

CSS Mode of S/PDIF TX0 |

IEC0 TX FREEZE |

0 |

RW |

Freeze S/PDIF TX0 Output Port |

60.11 Valid Bit for S/PDIF TX0 (iec0 valid out)

Address: 0x9C001E2C Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

G60A11 reserved0 |

31:1 |

RO |

RESERVED |

IEC0 VALID OUT |

0 |

RW |

Valid Bit |

60.12Channel Status of S/PDIF TX0 (iec0 par0 out)

Address:0x9C001E30

Reset: 0x0000 0000

Field NameBitAccessDescription

31:0 |

RW |

1st to 32th Bit of Channel Status |

|

|

IEC TX. Each frame(one L/R channel pair) are the same |

|

|

channel status. |

|

|

31th to 24th: |

|

|

bit31: 25th bit of channel status |

|

|

bit30: 26th bit of channel status |

|

|

bit29: 27th bit of channel status |

|

|

bit28: 28th bit of channel status |

|

|

bit27: 29th bit of channel status |

|

|

bit26: 30th bit of channel status |

|

|

bit25: 31th bit of channel status |

|

|

bit24: 32th bit of channel status |

|

|

23th to 16th: |

|

|

bit23: 17th bit of channel status |

|

|

bit22: 18th bit of channel status |

|

|

bit21: 19th bit of channel status |

|

|

bit20: 20th bit of channel status |

|

|

bit19: 21th bit of channel status |

|

|

bit18: 22th bit of channel status |

|

|

bit17: 23th bit of channel status |

|

|

bit16: 24th bit of channel status |

|

|

9th to 16th: |

|

|

bit15: 9th bit of channel status |

|

|

bit14: 10th bit of channel status |

|

|

bit13: 11th bit of channel status |

|

|

bit12: 12th bit of channel status |

|

|

bit11: 13th bit of channel status |

|

|

bit10: 14th bit of channel status |

|

|

bit09: 15th bit of channel status |

|

|

bit08: 16th bit of channel status |

|

|

1st to 8th: |

|

|

bit07: 1st bit of channel status |

|

|

bit06: 2nd bit of channel status |

|

|

bit05: 3rd bit of channel status |

|

|

bit04: 4th bit of channel status |

|

|

bit03: 5th bit of channel status |

|

|

bit02: 6th bit of channel status |

|

|

bit01: 7th bit of channel status |

|

|

bit00: 8th bit of channel status |

iec0 par0 out

60.13Channel Status of S/PDIF TX0 (iec0 par1 out)

Address:0x9C001E34

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A13 reserved031:16RO RESERVED

Reserved for further usage.

iec0 par1 out 15:0 RW 33th to 48th Bit of Channel Status

IEC TX frame 49 to 192 channel status all zeros.

41th to 48th:

bit15: 41th bit of channel status bit14: 42th bit of channel status bit13: 43th bit of channel status bit12: 44th bit of channel status bit11: 45th bit of channel status bit10: 46th bit of channel status bit09: 47th bit of channel status bit08: 48th bit of channel status

33th to 40th:

bit07: 33th bit of channel status bit06: 34th bit of channel status bit05: 35th bit of channel status bit04: 36th bit of channel status bit03: 37th bit of channel status bit02: 38th bit of channel status bit01: 39th bit of channel status bit00: 40th bit of channel status

60.14 Valid Bit for S/PDIF TX1 (iec1 valid out)

Address:0x9C001E38

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A14 reserved031:1RO RESERVED

Reserved for further usage.

IEC1 VALID OUT |

0 |

RW |

|

Valid Bit |

|

|

|

Valid bit of S/PDIF status information. Pratically, it is used |

|

|

|

|

to indicates the data type. |

|

|

|

|

0: PCM Data. |

|

|

|

|

1: RAW data. |

|

60.15Channel Status of S/PDIF TX1 (iec1 par0 out)

Address: 0x9C001E3C Reset: 0x0000 0000

Field NameBitAccessDescription

iec1 par0 out 31:0 RW 1st to 32th Bit of Channel Status

Please reference Address 12 iec0 par0 out.

60.16Channel Status of S/PDIF TX1 (iec1 par1 out)

Address:0x9C001E40

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A16 reserved031:16RO RESERVED

Reserved for further usage.

iec1 par1 out 15:0 RW 33th to 48th Bit of Channel Status

Please reference Address 13 iec0 par1 out.

60.17Debug Information of S/PDIF RX0 (iec0 rx debug info)

Address:0x9C001E44

Reset: 0x0000 0000

Field NameBitAccessDescription

IEC0 SAMPLE RATE CNT 31:20RO hardware use crystal 27M to count sampling rate

Ref. to Formula: FS = 27000 / IEC0 SAMPLE RATE CNT. (Unit: KHz)

G60A17 reserved119RO RESERVED

Reserved for further usage.

IEC0 VALID OUT DLY |

18 |

RU |

S/PDIF TX0 Valid Bit |

IEC0 PARITY ERR |

17 |

RO |

Parity Error |

IEC0 DEC ERR |

16 |

RUW |

Decode Error |

G60A17 reserved0 |

15:11 |

RO |

RESERVED |

IEC0 PERIOD 8T |

10:0 |

RO |

S/PDIF RX 0 Sample Rate Detect |

60.18 Valid Bit of S/PDIF RX0 (iec0 valid in)

Address:0x9C001E48

Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

G60A18 reserved0 |

31:1 |

RO |

RESERVED |

IEC0 VALID IN |

0 |

RO |

Valid Bit |

60.19Channel Status of S/PDIF RX0 (iec0 par0 in)

Address: 0x9C001E4C Reset: 0x0000 0000

Field NameBitAccessDescription

31:0 |

RO |

1st to 32th Bit of Channel Status (read only) |

|

|

IEC RX. Each frame(one L/R channel pair) are the same |

|

|

channel status. |

|

|

31th to 24th: |

|

|

bit31: 25th bit of channel status |

|

|

bit30: 26th bit of channel status |

|

|

bit29: 27th bit of channel status |

|

|

bit28: 28th bit of channel status |

|

|

bit27: 29th bit of channel status |

|

|

bit26: 30th bit of channel status |

|

|

bit25: 31th bit of channel status |

|

|

bit24: 32th bit of channel status |

|

|

23th to 16th: |

|

|

bit23: 17th bit of channel status |

|

|

bit22: 18th bit of channel status |

|

|

bit21: 19th bit of channel status |

|

|

bit20: 20th bit of channel status |

|

|

bit19: 21th bit of channel status |

|

|

bit18: 22th bit of channel status |

|

|

bit17: 23th bit of channel status |

|

|

bit16: 24th bit of channel status |

|

|

9th to 16th: |

|

|

bit15: 9th bit of channel status |

|

|

bit14: 10th bit of channel status |

|

|

bit13: 11th bit of channel status |

|

|

bit12: 12th bit of channel status |

|

|

bit11: 13th bit of channel status |

|

|

bit10: 14th bit of channel status |

|

|

bit09: 15th bit of channel status |

|

|

bit08: 16th bit of channel status |

|

|

1st to 8th: |

|

|

bit07: 1st bit of channel status |

|

|

bit06: 2nd bit of channel status |

|

|

bit05: 3rd bit of channel status |

|

|

bit04: 4th bit of channel status |

|

|

bit03: 5th bit of channel status |

|

|

bit02: 6th bit of channel status |

|

|

bit01: 7th bit of channel status |

|

|

bit00: 8th bit of channel status |

IEC0 PAR0 IN

60.20Channel Status of S/PDIF RX0 (iec0 par1 in)

Address:0x9C001E50

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A20 reserved031:16RO RESERVED

Reserved for further usage.

IEC0 PAR1 IN 15:0RO 33th to 48th Bit of Channel Status (Read only)

41th to 48th:

bit15: 41th bit of channel status bit14: 42th bit of channel status bit13: 43th bit of channel status bit12: 44th bit of channel status bit11: 45th bit of channel status bit10: 46th bit of channel status bit09: 47th bit of channel status bit08: 48th bit of channel status

33th to 40th:

bit07: 33th bit of channel status bit06: 34th bit of channel status bit05: 35th bit of channel status bit04: 36th bit of channel status bit03: 37th bit of channel status bit02: 38th bit of channel status bit01: 39th bit of channel status bit00: 40th bit of channel status

60.21Debug Information of S/PDIF RX1 (iec1 rx debug info)

Address:0x9C001E54

Reset: 0x0000 0000

Field NameBitAccessDescription

IEC1 SAMPLE RATE CNT 31:20RO hardware use crystal 27M to count sampling rate

Ref. to Formula: FS = 27000 / IEC1 SAMPLE RATE CNT. (Unit: KHz)

G60A21 reserved119RO RESERVED

Reserved for further usage.

IEC1 VALID OUT DLY |

18 |

RU |

S/PDIF TX1 Valid Bit |

IEC1 PARITY ERR |

17 |

RO |

Parity Error |

IEC1 DEC ERR |

16 |

RO |

Decode Error |

G60A21 reserved0 |

15:11 |

RO |

RESERVED |

IEC1 PERIOD 8T |

10:0 |

RO |

S/PDIF RX1 Sample Rate Detect |

60.22 Valid Bit of S/PDIF RX1 (iec1 valid in)

Address:0x9C001E58

Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

G60A22 reserved0 |

31:1 |

RO |

RESERVED |

IEC1 VALID IN |

0 |

RO |

Valid Bit |

60.23Channel Status of S/PDIF RX1 (iec1 par0 in)

Address: 0x9C001E5C Reset: 0x0000 0000

Field NameBitAccessDescription

IEC1 PAR0 IN 31:0RO 1st to 32th Bit of Channel Status

Please reference Address 19 iec0 par0 in.

60.24Channel Status of S/PDIF RX1 (iec1 par1 in)

Address:0x9C001E60

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A24 reserved031:16RO RESERVED

Reserved for further usage.

IEC1 PAR1 IN 15:0RO 33th to 48th Bit of Channel Status

Please reference Address 20 iec0 par1 in.

60.25Debug Information of S/PDIF RX2 (iec2 rx debug info)

Address:0x9C001E64

Reset: 0x0000 0000

Field NameBitAccessDescription

IEC2 SAMPLE RATE CNT 31:20RO hardware use crystal 27M to count sampling rate

Ref. to Formula: FS = 27000 / IEC2 SAMPLE RATE CNT. (Unit: KHz)

G60A25 reserved119:18RO RESERVED

Reserved for further usage. IEC2 PARITY ERR17RO Parity Error

Even parity check error.

IEC2 DEC ERR16RO Decode Error

Preamble Detection Error. G60A25 reserved015:11RO RESERVED

Reserved for further usage.

IEC2 PERIOD 8T10:0RO S/PDIF RX2 Sample Rate Detect

Report the S/PDIF input sample rate by sysclk clock cycles and times 8.

60.26 Valid Bit of S/PDIF RX2 (iec2 valid in)

Address:0x9C001E68

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A26 reserved0 |

31:1 |

RO |

RESERVED |

IEC2 VALID IN |

0 |

RO |

Valid Bit |

60.27Channel Status of S/PDIF RX2 (iec2 par0 in)

Address: 0x9C001E6C Reset: 0x0000 0000

Field NameBitAccessDescription

IEC2 PAR0 IN 31:0RO 1st to 32th Bit of Channel Status

Please reference Address 19 iec0 par0 in.

60.28Channel Status of S/PDIF RX2 (iec2 par1 in)

Address:0x9C001E70

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A28 reserved031:16RO RESERVED

Reserved for further usage.

IEC2 PAR1 IN 15:0RO 33th to 48th Bit of Channel Status

Please reference Address 20 iec0 par0 in.

60.29SACD Channel Number (Reserved) (G60ADDR29 reserved)

Address:0x9C001E74

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A29 reserved031:0RO reserved

60.30IEC Tx User FIFO Data (iec tx user wdata)

Address:0x9C001E78

Reset: 0x0000 0000

Field NameBitAccessDescription

G60A30 reserved031:16RO reserved

iec user wdata 15:0 RW IEC Tx User FIFO Data

Write user data to this register and than tirgger write strobe to push data to user FIFO.

60.31IEC Tx User FIFO Control (iec tx user ctrl)

Address: 0x9C001E7C Reset: 0x0000 0044

Field NameBitAccessDescription

iec1 user cnt31:24RO IEC1 Tx User FIFO Count

Current data count of user FIFO. The maxmum value is 64. iec0 user cnt23:16RO IEC0 Tx User FIFO Count

Current data count of user FIFO. The maxmum value is 64.

G60A31 reserved115:7RO reserved

iec1 user rst 6 RW IEC1 Tx User FIFO Reset

Level reset. When this reset bit is 1, iec1 user en is ignored.

0: Normal mode

1: Reset

iec1 user en5other IEC1 Tx User FIFO Enable

When iec1 user rst is 1, this enable bit is cleared to 0.

0: Disable

1: Enable

iec1 user we 4other IEC1 Tx User FIFO Write Enable

Write strobe of user FIFO. It is auto cleared at next cycle. G60A31 reserved03RO reserved

iec0 user rst 2 RW IEC0 Tx User FIFO Reset

Level reset. When this reset bit is 1, iec0 user en is ignored.

0: Normal mode

1: Reset

iec0 user en |

1 |

other |

IEC0 Tx User FIFO Enable |

iec0 user we |

0 |

other |

IEC0 Tx User FIFO Write Enable |

PChip Group 61AUD REG G1

AUD Group 1 Registers.

61.0ADCPRC Configuration Group 1 (adcp ch enable)

Address:0x9C001E80

Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

|

G61A0 reserved0 |

31:4 |

RO |

RESERVED |

|

ADCP CH ENABLE |

3:0 |

RW |

ADCPRC Channel Enable |

|

61.1ADCPRC Configuration Group 2 (adcp fubypass)

Address:0x9C001E84

Reset: 0x0000 7777

Field Name |

BitAccess |

Description |

G61A1 reserved0 |

31:16RO |

RESERVED |

ADCP CH3 CONFIG |

15:12 RW |

ADCP Channel 3 Configuration default all function are bypass. bit 3: Reserved. |

ADCP CH2 CONFIG |

11:8 |

RW |

ADCP Channel 2 Configuration default all function are bypass. bit 3: Reserved. |

ADCP CH1 CONFIG |

7:4 |

RW |

ADCP Channel 1 Configuration default all function are bypass. bit 3: Reserved. |

ADCP CH0 CONFIG |

3:0 |

RW |

ADCP Channel 0 Configuration default all function are bypass. bit 3: Reserved. |

61.2ADCPRC Mode Control (adcp mode ctrl)

Address:0x9C001E88

Reset: 0x0000 0000

Field NameBitAccessDescription

G61A2 reserved131:10RO RESERVED

Reserved for further usage. MIC STEREO ON 9 RW Mic Stereo Enable

0: Mic fifo is mono (default)

1: Mic fifo is stereo

LINEIN PATH SEL8 RW Line-in Path Select

Set 1 to select adcp ch2/3 for line-in source. Set 0 to select ch0/1 for line-in source, which is just like QAE377.

0: 377 mode (default)

1: Full function mode

G61A2 reserved07:5RO RESERVED

Reserved for further usage.

ADCP MICUP RATIO |

4:3 |

RW |

Up-Sample Ratio of Up Sampling on Mic |

ADCP B12MODE |

2 |

RW |

Reserved |

ADCP ECHODN RATIO |

1:0 |

RW |

Down-Sample Ratio of Down Sampling on Mic to Echo |

61.3ADCP Initialization Control (adcp init ctrl)

Address: 0x9C001E8C Reset: 0x0000 0000

Field NameBitAccessDescription

G61A3 reserved031:14RO RESERVED

Reserved for further usage. ADCP MIC MUTE 13 RW Mic Mute Enable

Active high to claim the mic output data to zero.

ADCP INIT BUSY12RU Initial Busy Flag

ADCP INITBUF 11W1C Buffer Initial

Initial delay buffers. Assert this bit to make hardware start to initilize buffers. This bit will be cleared at next clock cycle.

adcp idx inc mode10 RW Index Increment Mode

Active high to enable the post increment of coefficient in- dex.

ADCP FU IDX |

9:6 |

RW |

Function Unit Index |

ADCP CH IDX |

5:4 |

RW |

Channel Index |

adcp coeff idx |

3:0 |

RW |

Coefficient Index |

61.4 Coefficient Data Input (adcp coeff din)

Address:0x9C001E90

Reset: 0x0000 0000

Field NameBitAccessDescription

G61A4 reserved031:24RO RESERVED

Reserved for further usage.

ADCP COEFF DIN 23:0 RW Coefficient Data Input

61.5ADCPRC AGC Configuration of Ch0/1 (adcp agc cfg)

Address:0x9C001E94

Reset: 0x0065 0200

Field NameBitAccessDescription

G61A5 reserved031:28RO RESERVED

Reserved for further usage.

ADCP STEPLEN0 |

27:24 |

RW |

Step Length |

|

|

|

|

ADCP ETH0 |

15:0 |

RW |

Energy Threshold of Turn-On |

61.6ADCPRC AGC Configuration of Ch2/3 (adcp agc cfg2)

Address:0x9C001E98

Reset: 0x0065 0200

Field Name |

BitAccess |

Description |

G61A6 reserved0 |

31:28RO |

RESERVED |

ADCP STEPLEN2 |

27:24 RW |

Step Length |

23:16 |

RW |

Energy Threshold of Turn-Off |

15:0 |

RW |

Energy Threshold of Turn-On |

ADCP ETH OFF2

ADCP ETH2

61.7ADCPRC System Gain0 (adcp gain 0)

Address: 0x9C001E9C Reset: 0x0080 0000

Field NameBitAccessDescription

G61A7 reserved031:24RO RESERVED

Reserved for further usage. ADCP SYS GAIN0 23:0 RW Fractional Gain

0 to 0x7FFFFFF.

61.8ADCP System Gain1 (adcp gain 1)

Address:0x9C001EA0

Reset: 0x0080 0000

Field NameBitAccessDescription

G61A8 reserved031:24RO RESERVED

Reserved for further usage. ADCP SYS GAIN1 23:0 RW Fractional Gain

0 to 0x7FFFFFF.

61.9ADCP System Gain2 (adcp gain 2)

Address:0x9C001EA4

Reset: 0x0080 0000

Field NameBitAccessDescription

G61A9 reserved031:24RO RESERVED

Reserved for further usage. ADCP SYS GAIN2 23:0 RW Fractional Gain

0 to 0x7FFFFFF.

61.10ADCP System Gain3 (adcp gain 3)

Address:0x9C001EA8

Reset: 0x0080 0000

Field NameBitAccessDescription

G61A10 reserved031:24RO RESERVED

Reserved for further usage. ADCP SYS GAIN3 23:0 RW Fractional Gain

0 to 0x7FFFFFF.

61.11ADCP RISC Gain (adcp risc gain)

Address: 0x9C001EAC Reset: 0x0000 1111

Field NameBitAccessDescription

G61A11 reserved331:15RO RESERVED

Reserved for further usage. ADCP RISC GAIN3 14:12 RW Integer Gain of Channel 3

Value from 0 to 7.

G61A11 reserved211RO RESERVED

Reserved for further usage. ADCP RISC GAIN2 10:8 RW Integer Gain of Channel 2

Value from 0 to 7.

G61A11 reserved1 |

7 |

RO |

RESERVED |

ADCP RISC GAIN1 |

6:4 |

RW |

Integer Gain of Channel 1 |

G61A11 reserved0 |

3 |

RO |

RESERVED |

ADCP RISC GAIN0 |

2:0 |

RW |

Integer Gain of Channel 0 |

61.12ADCPRC Microphone-in Left Channel Data (adcp mic l)

Address:0x9C001EB0

Reset: 0x0000 0000

Field NameBitAccessDescription

G61A12 reserved031:24RO RESERVED

Reserved for further usage.

ADCP MIC L 23:0RO ADCPRC Microphone-in Left Channel Data

61.13ADCPRC Microphone-in Right Channel Data (adcp mic r)

Address:0x9C001EB4

Reset: 0x0000 0000

Field NameBitAccessDescription

G61A13 reserved031:24RO RESERVED

Reserved for further usage.

ADCP MIC R23:0RO ADCPRC Microphone-in Right Channel Data

61.14ADCPRC AGC Gain (adcp agc gain)

Address:0x9C001EB8

Reset: 0x0000 0000

Field NameBitAccessDescription

G61A14 reserved3 |

31 |

RO |

RESERVED |

ADGAIN CH3 |

30:24 |

RO |

Ch3 AGC Gain |

G61A14 reserved2 |

23 |

RO |

RESERVED |

ADGAIN CH2 |

22:16 |

RO |

Ch2 AGC Gain |

G61A14 reserved1 |

15 |

RO |

RESERVED |

ADGAIN CH1 |

14:8 |

RO |

Ch1 AGC Gain |

G61A14 reserved0 |

7 |

RO |

RESERVED |

ADGAIN CH0 |

6:0 |

RO |

Ch0 AGC Gain |

61.15 Reserved (G61ADDR15 reserved)

Address: 0x9C001EBC Reset: 0x0000 0000

Field NameBitAccessDescription

G61A15 reserved031:0RO reserved

61.16Audio Playback Timer Mode (aud apt mode)

Address:0x9C001EC0

Reset: 0x0000 0001

Field Name |

Bit |

Access |

Description |

G61A16 reserved0 |

31:5 |

RO |

RESERVED |

new pts flag |

4 |

RU |

New PTS Cmd Valid |

set new pts flag |

3:2 |

WO |

Set New Cmd Flag |

apt mode |

1:0 |

RW |

Audio Playback Timer Mode |

Set 1 to reset APT DATA (level trigger). Besides,

APT DATA stops counting in this model. (default)

Set 2 to stop counting. This register can not be written un- less you set it to stop mode. Please set it to mode 0 before enabling FIFO to ensure that no FIFO request is missed by playback timer.

0x0: counting mode (APT DATA is read only)

0x1: reset mode (APT DATA is read only) (default)

0x2: stop mode (APT DATA is R/W)

0x3: Reserved.

61.17Audio Playback Timer (aud apt data)

Address:0x9C001EC4

Reset: 0x0000 0000

Field NameBitAccessDescription

APT DATA 31:0RUW Audio Playback Timer

This timer converts audio playback count into STC (90khz)

clock domain. 32-bit unsigned integer. It is read only when apt mode is not 2.

61.18Audio Playback Timer Parameter (aud apt parameter)

Address:0x9C001EC8

Reset: 0x0000 0000

Field NameBitAccessDescription

APT SAMPLE NUM 31:16 RW Sample Number

This parameter defines how long we should add remain- der to APT. If sample number is 49 then remainder param- eter will be added to play time register every 49 samples.

16-bit unsigned integer

APT INT REMAINDER 15:12 RW Integer Part of Remainder

This value will be added to play time every segment. 0 to

7

APT FRAC REMAINDER 11:8 RW Fractional Part of Remainder

This value will be added to play time every segment. 0 to

7

APT INT DELTA 7:4 RW Integer Part of Delta

This value will be added to play time whenever an audio sample is played from PCM FIFO.0 to FIFO.7

APT FRAC DELTA 3:0 RW Fractional Part of Delta

This value will be added to play time whenever an audio sample is played from PCM FIFO.0 to FIFO.7

61.19DRAM Base Address Offset2 (aud audhwya2)

Address: 0x9C001ECC Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

AUDHWYA2 |

31:7 |

RW |

DRAM Base Address Offset for AUD Hardware |

G61A19 reserved0 |

6:0 |

RO |

RESERVED |

61.20DRAM Base Address Offset (aud audhwya)

Address:0x9C001ED0

Reset: 0x0000 0000

Field Name |

Bit |

Access |

Description |

AUDHWYA |

31:7 |

RW |

DRAM Base Address Offset for AUD Hardware |

G61A20 reserved0 |

6:0 |

RO |

RESERVED |

61.21DMA Counter Increment/Decrement (aud inc 0)

Address:0x9C001ED4

Reset: 0x0000 0000

Field Name |

BitAccess |

Description |

G61A21 reserved0 |

31:21 Other |

RESERVED |

DMACTL CNT INC0 |

20:0 Other |

FIFO NO.0 NO.9 Increment / FIFO NO.10 NO.20 Decre- ment |

61.22Delta Value (aud delta 0)

Address:0x9C001ED8

Reset: 0x0000 0000

Field NameBitAccessDescription

G61A22 reserved131:24RO RESERVED