29. MailBox

29.1 Introduction

Mailbox provides CA7 and ARM926 to transfer data to each other through RGST and Interrupt. Both directions support the first type of communication (Remote Function Call) and the second type of communication (Latency Sensitive).

On the RGST, two Register Groups are planned for data transfer in CA7 -> ARM926 and ARM926 -> CA7.

- Group 258: Provided CA7 -> ARM926 transfer data usage.

- Group 259: Provided ARM926 -> CA7 transfer data usage.

29.2 Function Diagram

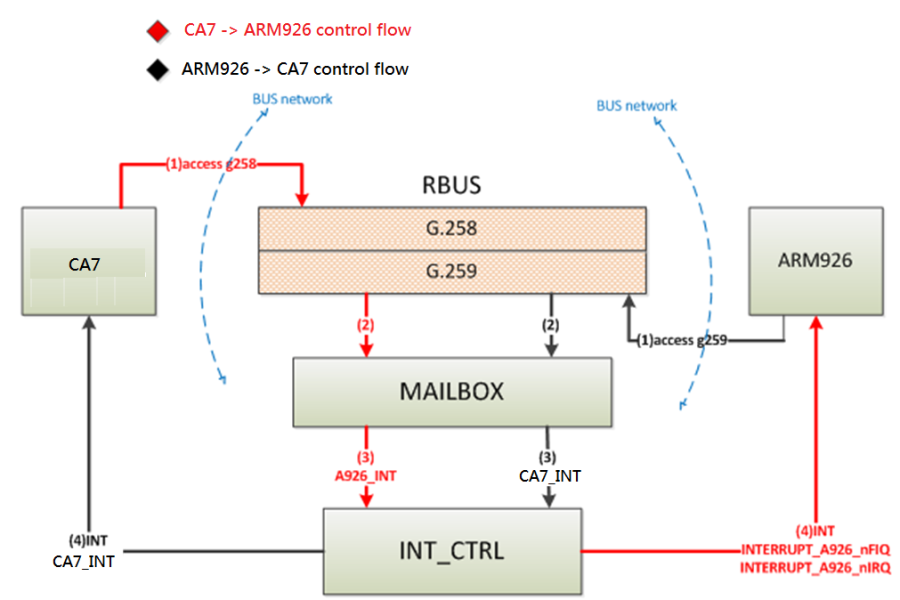

A generalized function diagram of MailBox is shown in Figure 29-1.

Figure 29-1 MailBox Functional Blocks

First Function Communication (Remote Function Call)

- CA7 continuously writes data to Group 258 (there are 20*32-bit registers in total), and is triggered by software operate Interrupt and notify ARM926.

- ARM926 continuously writes data to Group 259 (there are 20*32-bit registers in total), triggered by software operate Interrupt and notify CA7.

The second type of communication (Latency Sensitive)

- CA7 will write data to Group 258 then trigger Interrupt to notify ARM926 that only 32-bit transmission is supported at a time.

- ARM926 writes data to Group 259 then triggers Interrupt notification CA7, which only supports 32-bit transmission at a time.

29.3 Firmware Architecture

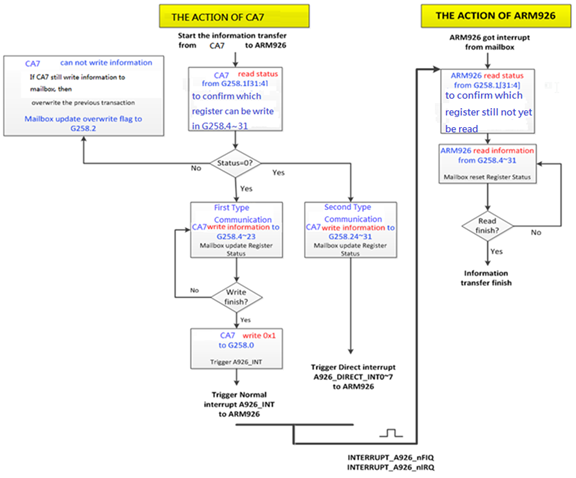

CA7 read status before write information / ARM926 read status before read information

- CA7 writes the information to be exchanged into G258.4~31, but before writing, read G258.1[31:4] first, and confirm that the Register Status corresponding to each register is unlocked before it can be written. It indicate that register data has been read by ARM926, can be written to overwrite; but if it is forced to write register with register status of 1, the MailBox is processed by overwriting the previous data. This part should be noted in use. At the same time, Mailbox will pull the corresponding bit of the register to be written in G258.2[31:4] to 1 as the record of transaction overwrite flag.

- Finally, according to the first type of communication or the second type of communication to trigger the corresponding interrupt, notify ARM926 to read G258.4~31. The first type of communication before ARM926 read G258.4~23, read G258.1 at first. Only the register corresponding to Register Status is 1 can be read. The second type of communication will first read the corresponding bit of G258.1 according to the interrupt, to confirm that Register Status is 1, and then read from the corresponding register.

Figure 29-2 MailBox Firmware Architecture1

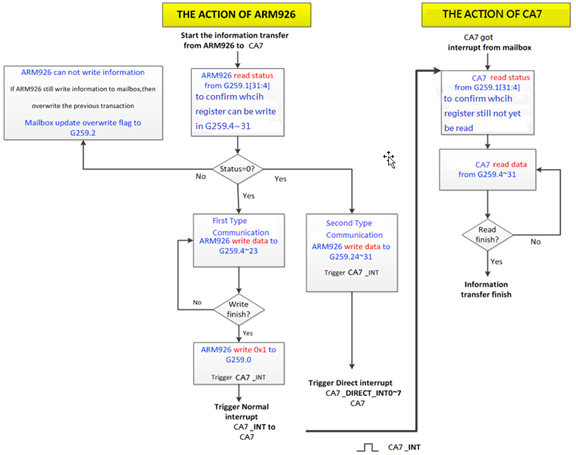

ARM926 read status before write information / CA7 read status before read information

- ARM926 writes the information to be exchanged into G259.4~31, but before writing, read G259.1[31:4] first, and confirm that the Register Status corresponding to each register is unlock. It indicates that register data has been read by CA7 and can be overwritten by the overlay. However, if the register with Register Status is 1 is forcibly written, the processing of MailBox is to overwrite the previous data. This part should be noted in use. At the same time, Mailbox will pull the corresponding bit of the register to be written in G259.2[31:4] to 1 as the record of transaction overwrite flag.

- Finally, trigger the corresponding interrupt according to the first type of communication or the second type of communication, and notify CA7 to read G259.4~31. The first type of communication should be before CA7 read G259.4~23, read G259.1 at first. Only read the register corresponding to Register Status is 1. The second type of communication will first read the corresponding bit of G259.1 according to the interrupt, to confirm the Register Status is 1, then read from the corresponding register.

Figure 29-3 MailBox Firmware Architecture2

29.4 Registers Map

29.4.1 Registers Memory Map

Address | Group No. | Register Name | Register Description |

0x9C008100 | G258.0 | Mbox_cpub_int_trigger | Trigger CPUB_INT |

0x9C008104 | G258.1 | Mbox0_writelock_flag | Monitor the writelock status of mailbox0 |

0x9C008108 | G258.2 | Mbox0_overwrite_flag | Monitor the overwrite status of mailbox0 |

0x9C00810C | G258.3 | RESERVED | |

0x9C008110 | G258.4 | Mbox0_normal_trans[0] | Normal data transfer from CPUA to CPUB |

~~ | ~~ | ~~ | ~~ |

0x9C00815C | G258.23 | Mbox0_normal_trans[19] | Normal data transfer from CPUA to CPUB |

0x9C008160 | G258.24 | Mbox0_direct_trans[0] | Direct data transfer from CPUA to CPUB |

~~ | ~~ | ~~ | ~~ |

0x9C00817C | G258.31 | Mbox0_direct_trans[7] | Direct data transfer from CPUA to CPUB |

Address | Group No. | Register Name | Register Description |

0x9C008180 | G259.0 | Mbox_cpua_int_trigger | Trigger CPUA_INT |

0x9C008184 | G259.1 | Mbox1_writelock_flag | Monitor the writelock status of mailbox1 |

0x9C008188 | G259.2 | Mbox1_overwrite_flag | Monitor the overwrite status of mailbox1 |

0x9C00818C | G259.3 | RESERVED | |

0x9C008190 | G259.4 | Mbox1_normal_trans[0] | Normal data transfer from CPUB to CPUA |

~~ | ~~ | ~~ | ~~ |

0x9C0081DC | G259.23 | Mbox1_normal_trans[19] | Normal data transfer from CPUB to CPUA |

0x9C0081E0 | G259.24 | Mbox1_direct_trans[0] | Direct data transfer from CPUB to CPUA |

~~ | ~~ | ~~ | ~~ |

0x9C0081FC | G259.31 | Mbox1_direct_trans[7] | Direct data transfer from CPUB to CPUA |

29.4.2 Registers Description

Group 258 Mailbox CPUA to CPUB

258.0 Trigger CPUB_INT (mbox_cpub_int_trigger)

Address: 0x9C008100

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:1 | RO | Reserved bits |

CPUB_INT | 0 | RW | Trigger CPUB_INT |

258.1 Mailbox0 Writelock Flag Monitor (mbox0_writelock_flag)

Address: 0x9C008104

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| mbox0_direct_writelock07 | 31 | RW | Monitor the writelock status of direct_reg07 When CPUA write direct_reg07, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock06 | 30 | RW | Monitor the writelock status of direct_reg06 When CPUA write direct_reg06, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock05 | 29 | RW | Monitor the writelock status of direct_reg05 When CPUA write direct_reg05, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock04 | 28 | RW | Monitor the writelock status of direct_reg04 When CPUA write direct_reg04, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock03 | 27 | RW | Monitor the writelock status of direct_reg03 When CPUA write direct_reg03, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock02 | 26 | RW | Monitor the writelock status of direct_reg02 When CPUA write direct_reg02, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock01 | 25 | RW | Monitor the writelock status of direct_reg01 When CPUA write direct_reg01, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_direct_writelock00 | 24 | RW | Monitor the writelock status of direct_reg00 When CPUA write direct_reg00, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock19 | 23 | RW | Monitor the writelock status of normal_reg19 When CPUA write normal_reg19, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock18 | 22 | RW | Monitor the writelock status of normal _reg18 When CPUA write normal _reg18, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock17 | 21 | RW | Monitor the writelock status of normal _reg17 When CPUA write normal _reg17, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock16 | 20 | RW | Monitor the writelock status of normal _reg16 When CPUA write normal _reg16, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock15 | 19 | RW | Monitor the writelock status of normal _reg15 When CPUA write normal _reg15, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock14 | 18 | RW | Monitor the writelock status of normal _reg14 When CPUA write normal _reg14, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock13 | 17 | RW | Monitor the writelock status of normal _reg13 When CPUA write normal _reg13, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock12 | 16 | RW | Monitor the writelock status of normal _reg12 When CPUA write normal _reg12, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock11 | 15 | RW | Monitor the writelock status of normal_reg11 When CPUA write normal_reg11, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock10 | 14 | RW | Monitor the writelock status of normal _reg10 When CPUA write normal _reg10, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock09 | 13 | RW | Monitor the writelock status of normal _reg09 When CPUA write normal _reg09, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock08 | 12 | RW | Monitor the writelock status of normal _reg08 When CPUA write normal _reg08, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock07 | 11 | RW | Monitor the writelock status of normal _reg07 When CPUA write normal _reg07, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock06 | 10 | RW | Monitor the writelock status of normal _reg06 When CPUA write normal _reg06, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock05 | 9 | RW | Monitor the writelock status of normal _reg05 When CPUA write normal _reg05, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock04 | 8 | RW | Monitor the writelock status of normal _reg04 When CPUA write normal _reg04, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock03 | 7 | RW | Monitor the writelock status of normal_reg03 When CPUA write normal_reg03, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock02 | 6 | RW | Monitor the writelock status of normal _reg02 When CPUA write normal _reg02, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock01 | 5 | RW | Monitor the writelock status of normal _reg01 When CPUA write normal _reg01, it will be locked until CPUB read this register 0: unlock 1: lock |

| mbox0_ normal _writelock00 | 4 | RW | Monitor the writelock status of normal _reg00 When CPUA write normal _reg00, it will be locked until CPUB read this register 0: unlock 1: lock |

| Reserved | 3:0 | RW | Reserved bits Not used |

258.2 Mailbox0 Overwrite Flag Monitor (mbox0_overwrite_flag)

Address: 0x9C008108

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| mbox0_direct_overwrite07 | 31 | RW | Monitor the overwrite status of direct_reg07 Assert this bit, when CPUA write direct_reg07, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite06 | 30 | RW | Monitor the overwrite status of direct_reg06 Assert this bit, when CPUA write direct_reg06, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite05 | 29 | RW | Monitor the overwrite status of direct_reg05 Assert this bit, when CPUA write direct_reg05, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite04 | 28 | RW | Monitor the overwrite status of direct_reg04 Assert this bit, when CPUA write direct_reg04, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite03 | 27 | RW | Monitor the overwrite status of direct_reg03 Assert this bit, when CPUA write direct_reg03, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite02 | 26 | RW | Monitor the overwrite status of direct_reg02 Assert this bit, when CPUA write direct_reg02, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite01 | 25 | RW | Monitor the overwrite status of direct_reg01 Assert this bit, when CPUA write direct_reg01, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_direct_overwrite00 | 24 | RW | Monitor the overwrite status of direct_reg00 Assert this bit, when CPUA write direct_reg00, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite19 | 23 | RW | Monitor the overwrite status of normal_reg19 Assert this bit, when CPUA write normal_reg19, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite18 | 22 | RW | Monitor the overwrite status of normal _reg18 Assert this bit, when CPUA write normal_reg18, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite17 | 21 | RW | Monitor the overwrite status of normal _reg17 Assert this bit, when CPUA write normal_reg17, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite16 | 20 | RW | Monitor the overwrite status of normal _reg16 Assert this bit, when CPUA write normal_reg16, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite15 | 19 | RW | Monitor the overwrite status of normal _reg15 Assert this bit, when CPUA write normal_reg15, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite14 | 18 | RW | Monitor the overwrite status of normal _reg14 Assert this bit, when CPUA write normal_reg14, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite13 | 17 | RW | Monitor the overwrite status of normal _reg13 Assert this bit, when CPUA write normal_reg13, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _overwrite12 | 16 | RW | Monitor the overwrite status of normal _reg12 Assert this bit, when CPUA write normal_reg12, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite11 | 15 | RW | Monitor the overwrite status of normal_reg11 Assert this bit, when CPUA write normal_reg11, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite10 | 14 | RW | Monitor the overwrite status of normal _reg10 Assert this bit, when CPUA write normal_reg10, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite09 | 13 | RW | Monitor the overwrite status of normal _reg09 Assert this bit, when CPUA write normal_reg09, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite08 | 12 | RW | Monitor the overwrite status of normal _reg08 Assert this bit, when CPUA write normal_reg08, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite07 | 11 | RW | Monitor the overwrite status of normal _reg07 Assert this bit, when CPUA write normal_reg07, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite06 | 10 | RW | Monitor the overwrite status of normal _reg06 Assert this bit, when CPUA write normal_reg06, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite05 | 9 | RW | Monitor the overwrite status of normal _reg05 Assert this bit, when CPUA write normal_reg05, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite04 | 8 | RW | Monitor the overwrite status of normal _reg04 Assert this bit, when CPUA write normal_reg04, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite03 | 7 | RW | Monitor the overwrite status of normal_reg03 Assert this bit, when CPUA write normal_reg03, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite02 | 6 | RW | Monitor the overwrite status of normal _reg02 Assert this bit, when CPUA write normal_reg02, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite01 | 5 | RW | Monitor the overwrite status of normal _reg01 Assert this bit, when CPUA write normal_reg01, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox0_ normal _ overwrite00 | 4 | RW | Monitor the overwrite status of normal _reg00 Assert this bit, when CPUA write normal_reg00, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| Reserved | 3:0 | RO | Reserved bits Not used |

258.3 Reserved (reserved)

Address: 0x9C00810C

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:0 | RO | Reserved bits |

258.4 Normal transaction00 from CPUA to CPUB (mbox0_normal_trans[0])

Address: 0x9C008110

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

mbox0_normal_reg00 | 31:0 | RW | Be used to transfer data from CPUA to CPUB by normal transaction |

258.5~258.23 map to normal transaction01~19, register define is same to 258.4

258.24 Direct transaction00 from CPUA to CPUB (mbox0_direct_trans[0])

Address: 0x9C008160

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

mbox0_direct_reg00 | 31:0 | RW | Be used to transfer data from CPUA to CPUB by direct transaction |

258.25~258.31 map to direct transaction01~07, register define is same to 258.24

Group 259 Mailbox CPUB to CPUA

259.0 Trigger CPUA_INT (mbox_cpua_int_trigger)

Address: 0x9C008180

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:1 | RO | Reserved bits |

CPUA_INT | 0 | RW | Trigger CPUA_INT |

259.1 Mailbox1 Writelock Flag Monitor (mbox1_writelock_flag)

Address: 0x9C008184

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| mbox1_direct_writelock07 | 31 | RW | Monitor the writelock status of direct_reg07 When CPUB write direct_reg07, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock06 | 30 | RW | Monitor the writelock status of direct_reg06 When CPUB write direct_reg06, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock05 | 29 | RW | Monitor the writelock status of direct_reg05 When CPUB write direct_reg05, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock04 | 28 | RW | Monitor the writelock status of direct_reg04 When CPUB write direct_reg04, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock03 | 27 | RW | Monitor the writelock status of direct_reg03 When CPUB write direct_reg03, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock02 | 26 | RW | Monitor the writelock status of direct_reg02 When CPUB write direct_reg02, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock01 | 25 | RW | Monitor the writelock status of direct_reg01 When CPUB write direct_reg01, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_direct_writelock00 | 24 | RW | Monitor the writelock status of direct_reg00 When CPUB write direct_reg00, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock19 | 23 | RW | Monitor the writelock status of normal_reg19 When CPUB write normal_reg19, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock18 | 22 | RW | Monitor the writelock status of normal _reg18 When CPUB write normal _reg18, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock17 | 21 | RW | Monitor the writelock status of normal _reg17 When CPUB write normal _reg17, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock16 | 20 | RW | Monitor the writelock status of normal _reg16 When CPUB write normal _reg16, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock15 | 19 | RW | Monitor the writelock status of normal _reg15 When CPUB write normal _reg15, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock14 | 18 | RW | Monitor the writelock status of normal _reg14 When CPUB write normal _reg14, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock13 | 17 | RW | Monitor the writelock status of normal _reg13 When CPUB write normal _reg13, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock12 | 16 | RW | Monitor the writelock status of normal _reg12 When CPUB write normal _reg12, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock11 | 15 | RW | Monitor the writelock status of normal_reg11 When CPUB write normal_reg11, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock10 | 14 | RW | Monitor the writelock status of normal _reg10 When CPUB write normal _reg10, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock09 | 13 | RW | Monitor the writelock status of normal _reg09 When CPUB write normal _reg09, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock08 | 12 | RW | Monitor the writelock status of normal _reg08 When CPUB write normal _reg08, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock07 | 11 | RW | Monitor the writelock status of normal _reg07 When CPUB write normal _reg07, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock06 | 10 | RW | Monitor the writelock status of normal _reg06 When CPUB write normal _reg06, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock05 | 9 | RW | Monitor the writelock status of normal _reg05 When CPUB write normal _reg05, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock04 | 8 | RW | Monitor the writelock status of normal _reg04 When CPUB write normal _reg04, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock03 | 7 | RW | Monitor the writelock status of normal_reg03 When CPUB write normal_reg03, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock02 | 6 | RW | Monitor the writelock status of normal _reg02 When CPUB write normal _reg02, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock01 | 5 | RW | Monitor the writelock status of normal _reg01 When CPUB write normal _reg01, it will be locked until CPUA read this register 0: unlock 1: lock |

| mbox1_ normal _writelock00 | 4 | RW | Monitor the writelock status of normal _reg00 When CPUB write normal _reg00, it will be locked until CPUA read this register 0: unlock 1: lock |

| Reserved | 3:0 | RW | Reserved bits Not used |

259.2 Mailbox1 Overwrite Flag Monitor (mbox1_overwrite_flag)

Address: 0x9C008188

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| mbox1_direct_overwrite07 | 31 | RW | Monitor the overwrite status of direct_reg07 Assert this bit, when CPUB write direct_reg07, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite06 | 30 | RW | Monitor the overwrite status of direct_reg06 Assert this bit, when CPUB write direct_reg06, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite05 | 29 | RW | Monitor the overwrite status of direct_reg05 Assert this bit, when CPUB write direct_reg05, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite04 | 28 | RW | Monitor the overwrite status of direct_reg04 Assert this bit, when CPUB write direct_reg04, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite03 | 27 | RW | Monitor the overwrite status of direct_reg03 Assert this bit, when CPUB write direct_reg03, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite02 | 26 | RW | Monitor the overwrite status of direct_reg02 Assert this bit, when CPUB write direct_reg02, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite01 | 25 | RW | Monitor the overwrite status of direct_reg01 Assert this bit, when CPUB write direct_reg01, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_direct_overwrite00 | 24 | RW | Monitor the overwrite status of direct_reg00 Assert this bit, when CPUBwrite direct_reg00, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite19 | 23 | RW | Monitor the overwrite status of normal_reg19 Assert this bit, when CPUB write normal_reg19, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite18 | 22 | RW | Monitor the overwrite status of normal _reg18 Assert this bit, when CPUB write normal_reg18, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite17 | 21 | RW | Monitor the overwrite status of normal _reg17 Assert this bit, when CPUB write normal_reg17, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite16 | 20 | RW | Monitor the overwrite status of normal _reg16 Assert this bit, when CPUB write normal_reg16, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite15 | 19 | RW | Monitor the overwrite status of normal _reg15 Assert this bit, when CPUB write normal_reg15, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite14 | 18 | RW | Monitor the overwrite status of normal _reg14 Assert this bit, when CPUB write normal_reg14, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite13 | 17 | RW | Monitor the overwrite status of normal _reg13 Assert this bit, when CPUB write normal_reg13, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _overwrite12 | 16 | RW | Monitor the overwrite status of normal _reg12 Assert this bit, when CPUB write normal_reg12, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite11 | 15 | RW | Monitor the overwrite status of normal_reg11 Assert this bit, when CPUB write normal_reg11, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite10 | 14 | RW | Monitor the overwrite status of normal _reg10 Assert this bit, when CPUB write normal_reg10, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite09 | 13 | RW | Monitor the overwrite status of normal _reg09 Assert this bit, when CPUB write normal_reg09, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite08 | 12 | RW | Monitor the overwrite status of normal _reg08 Assert this bit, when CPUB write normal_reg08, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite07 | 11 | RW | Monitor the overwrite status of normal _reg07 Assert this bit, when CPUB write normal_reg07, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite06 | 10 | RW | Monitor the overwrite status of normal _reg06 Assert this bit, when CPUB write normal_reg06, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite05 | 9 | RW | Monitor the overwrite status of normal _reg05 Assert this bit, when CPUB write normal_reg05, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite04 | 8 | RW | Monitor the overwrite status of normal _reg04 Assert this bit, when CPUB write normal_reg04, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite03 | 7 | RW | Monitor the overwrite status of normal_reg03 Assert this bit, when CPUB write normal_reg03, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite02 | 6 | RW | Monitor the overwrite status of normal _reg02 Assert this bit, when CPUB write normal_reg02, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite01 | 5 | RW | Monitor the overwrite status of normal _reg01 Assert this bit, when CPUB write normal_reg01, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| mbox1_ normal _ overwrite00 | 4 | RW | Monitor the overwrite status of normal _reg00 Assert this bit, when CPUB write normal_reg00, which is already in writelock state 0: clear overwrite status 1: reg is overwrtten |

| Reserved | 3:0 | RW | Reserved bits Not used |

259.3 Reserved (reserved)

Address: 0x9C00818C

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:0 | RO | Reserved bits |

259.4 Normal transaction00 from CPUB to CPUA (mbox1_normal_trans[0])

Address: 0x9C008190

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

mbox1_normal_reg00 | 31:0 | RW | Be used to transfer data from CPUB to CPUA by normal transaction |

259.5~259.23 map to normal transaction01~19, register define is same to 259.4

259.24 Direct transaction00 from CPUB to CPUA (mbox1_direct_trans[0])

Address: 0x9C0081E0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

mbox1_direct_reg00 | 31:0 | RW | Be used to transfer data from CPUB to CPUA by direct transaction |

259.25~259.31 map to direct transaction01~07, register define is same to 259.24