14. Universal Serial Bus (USB)

14.1 Introduction

The USB is specified to be an industry-standard extension to the PC architecture. It provides an USB compliant connection between the host PC and the function implemented by the microcontroller. It also supports USB-OTG (On-The-Go) function to connect with peripheral USB devices. Data transfer between the host PC and the system memory occurs through a dedicated packet buffer memory accessed directly by the USB peripheral. The size of this dedicated buffer memory must be according to the number of endpoints used and maximum packet size. The dedicated memory is sized to 512bytes and up to 16 mono-directional endpoints can be used. This USB supports 4 kind endpoint transactions, they are Control, Bulk, Interrupt and Isochronous transfer mode.

A USB system is described by three definitional areas, USB PHY (UPHY) , USB Controller System (USBC) and On-The-Go (OTG) Controller. Where USB Controller system includes two major parts: USB host controller(UHC) and USB device controller(UDC). The USB transfer signals and power over a four-wire cable, the signaling occurs over wires on each point-to-point segment.

The USB HOST IP (UHC) is a USB2.0 Host Controller, Support both Enhanced Host Controller Interface (EHCI) and Open Host Controller Interface (OHCI), 32bit AHB/AXI configure bus, 64bit AXI data bus. The USB DEVICE IP (UDC) is a standard USB Device Controller which supports USB2.0 High Speed and Full speed, AXI Master bus, AXI Master1 bus (used for ISO auto DMA), AHB slave bus and UTMI (USB2.0 Transceiver Macrocell Interface) interface. The USB PHY module supports working in Host or Device mode and can dynamic switch.

The USB control registers located in the memory map address range of 9c102000h~9c103fffh. The USB PHY control registers located in the 9c004a80h~9c004b7fh. SP7021 totally supports two USB2.0 modules, the features list as below.

- UTMI+ level3 compatible with OTG

- 27MHz crystal input to support Battery Charger and sync signals

- Integrated Phase-Locked Loop (PLL) oscillator generate 120M CLK to DPHY

- Supports various power down modes include Operating, Partial and Suspend modes

- Supports high-speed (HS, 480 Mbps), full-speed (FS, 12Mbps) and low-speed (LS, 1.5Mbps) data transfer rates

- OTG supports Attach Detection Protocol (ADP), Session Request Protocol (SRP) and Host Negotiation Protocol (HNP)

- Support boot from each USB port

- Support USB video class (UVC)

14.2 Function Diagram

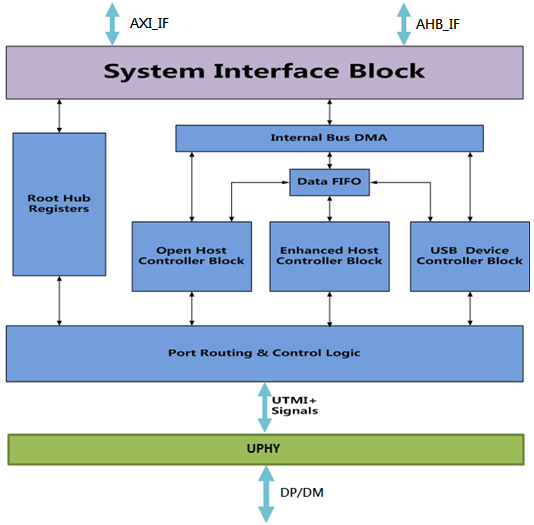

A generalized function diagram of USB is shown in Figure 14-1.

Figure 14-1 USB Functional Blocks

- AHB_IF: Advanced High-performance Bus (AHB) Interface block, used as AHB bus master data and configure register

- AXI_IF: Advanced Extensible Interface (AXI) block, used for high performance read, write and address access.

- Enhanced Host Controller Block(EHCI): Standard Enhanced Host Controller Interface IP.

- Open Host Controller Block(OHCI): Standard Open Host Controller Interface IP.

- USB Device Controller Block(UDC): SUNPLUS USB Device Controller IP.

- Hub Configure registers(RHREG): Root Hub Configure registers block

- PORT Routing & Control Logic: Generate PHY Control signals (UTMI).

- UPHY: Convert parallel data of UTMI into serial data, and output to the outside of the chip through differential data lines.

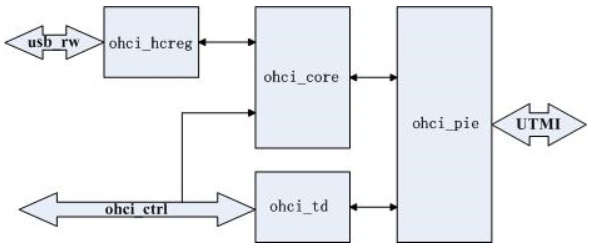

14.2.1 OHCI Block Diagram

The EHCI has the same structure as OHCI, so below description will focus on OHCI block. Figure 14-2 shows generic OHCI Block Diagram.

Figure 14-2 OHCI Block Diagram

- ohci_reg: This is OHCI register control block. Use the AHB master to read/write the OHCI register which generate control signal to OHCI.

- ohci_td: This is OHCI data structure process block. The TD is Transfer Descriptor of OHCI.

- ohci_core: This is OHCI main block, used to R/W ED (Endpoint Descriptor) and TD, and control USB Transfers.

- ohci_pie: This block is used to control USB port state, such as reset、suspend and resume, generate port control signals.

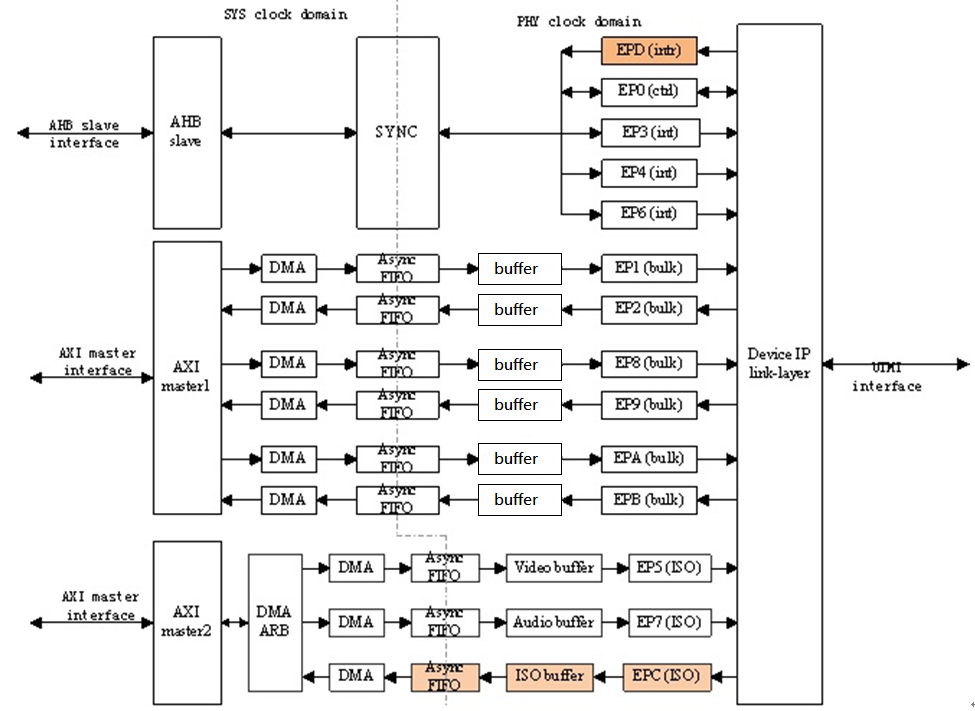

14.2.2 USB Device Controller (UDC) Block Diagram

Figure 14-3 shows a generic UDC Block Diagram.

Figure 14-3 UDC Block Diagram

- AXI master1:

- Receive the command from USB and issue AXI transition

- It contains 1*audio DMA, 1*video DMA and 3*bulk DMA

- It contains the DMA arbitration mechanism

- AXI master2:

- Including AXI transition control for ISO auto DMA mode

- AHB slave:

- receive the command from system and issue AHB transition

- It contains the configure registers, CPU can write or read these registers by AHB bus

- DMA: DMA logic, issue data transition

- ISO DMA: ISO auto DMA block

- Including ISO IN and ISO OUT DMA control for TRB and Data Read/Write

- Including DMA arbitration mechanism

- SYNC: Sync logic between SYS clock domain and PHY clock domain

- Async FIFO: Sync data between the two clock domain

- Buffer: data buffer

- EPx: EPx (Endpoint x) control logic

- Device IP Link-layer: USB link layer transition logic

- EP5 DMA: ISO IN DMA for Endpoint5

- EP7 DMA: ISO IN DMA for Endpoint7

- EPC DMA: ISO OUT DMA for EndpointC

- DMA ARB: DMA Arbiter for ISO Endpoints

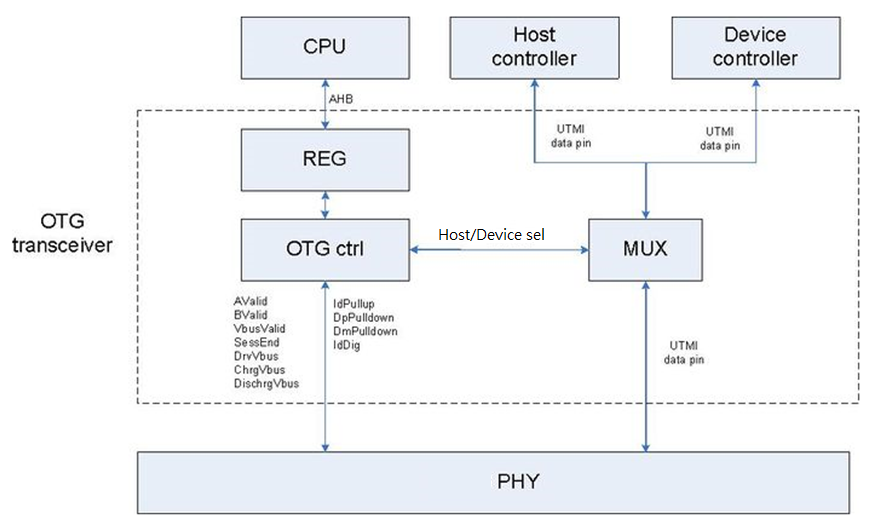

14.2.3 OTG Transceiver Block Diagram

Figure 14-4 shows a generic OTG Transceiver Block Diagram.

Figure 14-4 OTG Transceiver Block Diagram

- REG: Receive the command from system and issue AHB transition. It contains the configure registers and CPU can read or write these registers by AHB bus.

- OTG ctrl: Provide flags to deal with OTG functions (SRP/HNP/ADP). It also provides select signal to MUX module.

- MUX: Select UTMI data to host controller or device controller.

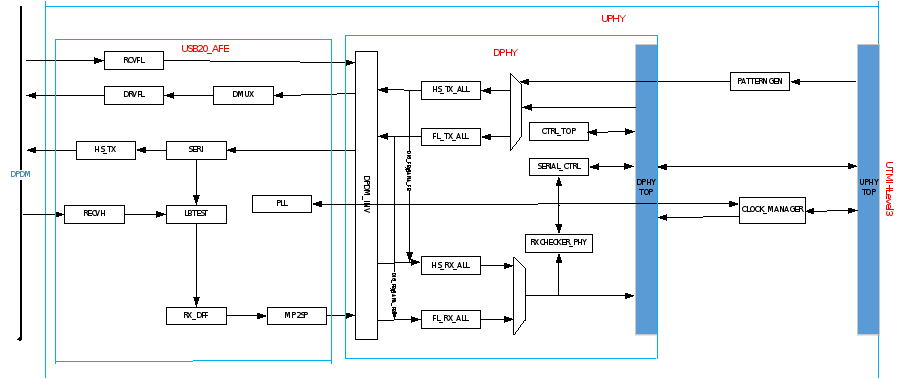

14.2.4 UPHY Block Diagram

Figure 14-5 shows a generic UPHY Block Diagram

Figure 14-5 UPHY Block Diagram

- FS_TX_ALL/HS_TX_ALL : Receive signals from the UTMI interface in full-speed, low-speed and high-speed mode, through bit stuffer and encode, then pass the buffer to the APHY

- FS_RX_ALL : Receive data from the APHY in full-speed or low-speed mode. After Decode and bit unstuffing, the data is converted to UTMI and output to Host or Device.

- HS_RX_ALL : In high-speed mode, 20bit data is accepted from the APHY, and the data is separated from the clock according to the CDR, and 5 bit data is sampled. After Decode and bit unstuffing, the data is output from the UTMI interface to Host or Device.

- PATTERNGEN: Generate test-related patterns through I2C or BIST mode

- CTRL_TOP :

- The TX/RX enable signal of HS/FS/LS is generated based on the UTMI signal.

- Output line state signal on UTMI interface

- Control pull-up and pull-down resistors on the DP/DM line

- In HS mode, generate HOST_DISC signal, HOST_DISC=0, device connection, HOST_DISC=1, device disconnected

- SERIAL_CTRL: Write or read register values to UPHY internally via I2C or RGST BUS mode

- CLOCK_MANAGER: Generate L120_CLK and UTMI_CLK. When suspend, generate PLL_OFF to turn off the PLL.

- RXCHECKER_PHY: Check if the data during transmission is correct

14.3 USB Host Controller

When insert a USB device, the USB host controller will trigger EHCI/OHCI interrupt to tell software that there is a USB device inserted.

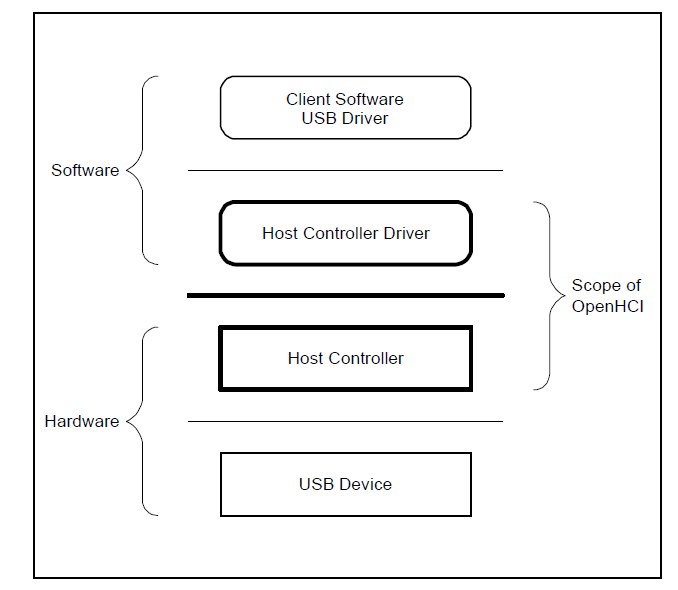

14.3.1 OHCI Controller

Figure 14-6 shows four main areas of a Universal Serial Bus system. These areas are the Client Software/USB Driver, Host Controller Driver (HCD), Host Controller (HC) and USB Device. OHCI specifies the interface between the Host Controller Driver and the Host Controller and the fundamental operation of each.

Figure 14-6 OHCI controller

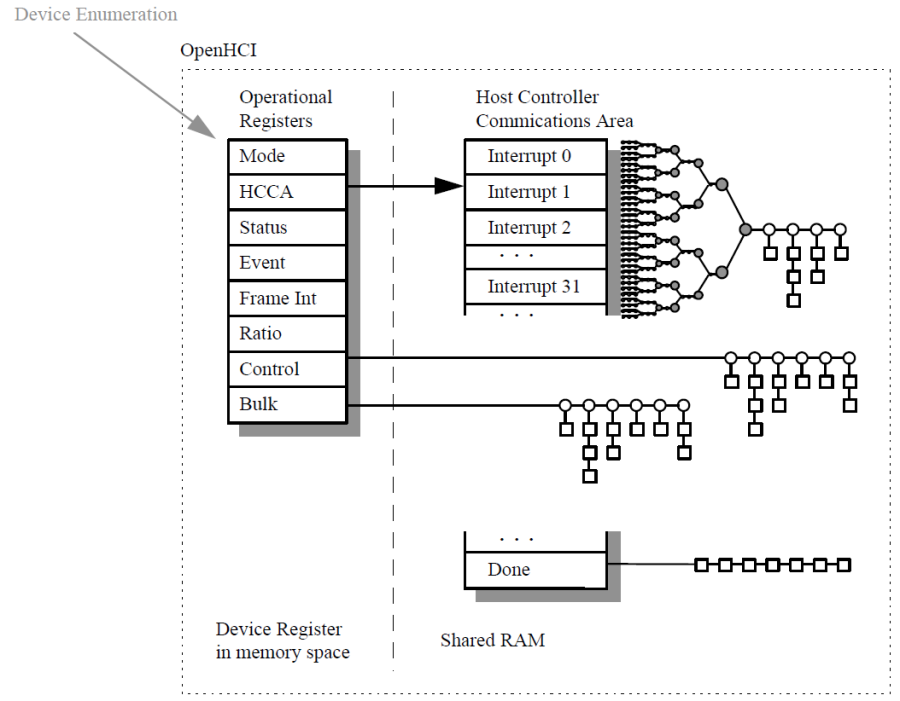

There are two communication channels between the Host Controller and the Host Controller Driver (Please refer to figure 14-7). The first channel uses a set of operational registers located on the HC. The Host Controller is the target for all communication on this channel. The operational registers contain control, status, and list pointer registers. Within the operational register set is a pointer to a location in shared memory named the Host Controller Communications Area (HCCA). The HCCA is the second communication channel. The Host Controller is the master for all communication on this channel. The HCCA contains the head pointers to the interrupt Endpoint Descriptor lists, the head pointer to the done queue, and status information associated with start-of-frame processing.

Figure 14-7 OHCI communication channel

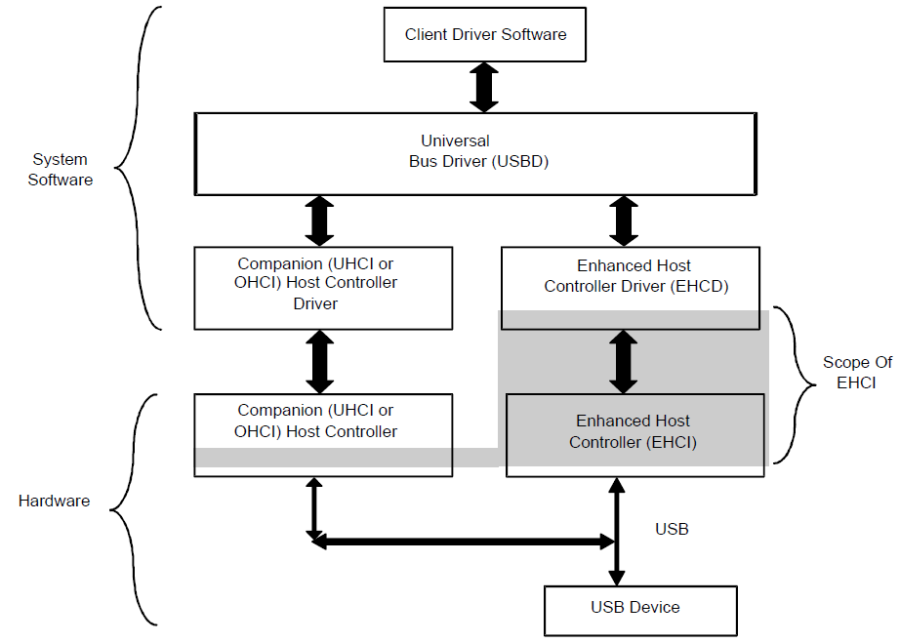

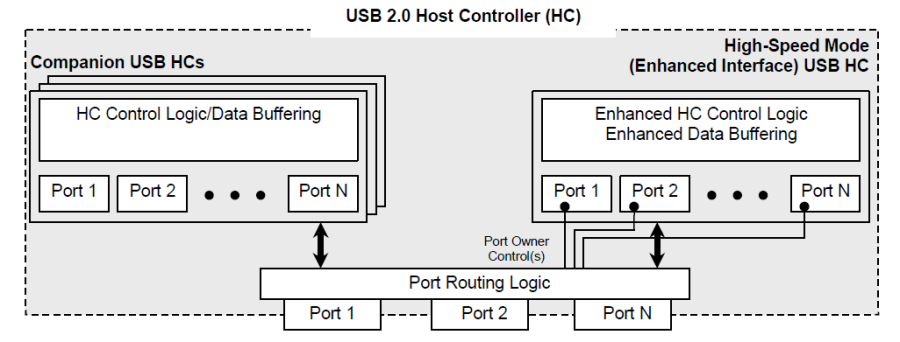

14.3.2 EHCI Controller

A USB Host System is composed of a number of hardware and software layers. The Figure 14-8 illustrates a conceptual block diagram of the building block layers in a host system that work in concert to support USB2.0.

Figure 14-8 EHCI controller

This architecture allows the USB 2.0 host controller to provide USB functionality as long as there is at least USB 1.1 software support in the resident operating system. Full USB 2.0 functionality is delivered when both USB 1.1 and EHCI software is available in the operating system. The port transceiver routing logic is key to delivering this flexible operating environment. The state of the routing logic initially depends on whether software has configured the EHCI controller. Once the EHCD driver has configured the EHCI controller, it can specifically release the transceiver to the companion host controller port register if the attached device is not a high-speed device. When the operating system does not include support for the EHCI controller, the ports are default-routed to the companion host controllers and existing USB support for Full- and Low-speed devices remains.

Figure 14-9 Companion Host Controller

The Companion Host Controller (CHC) may be any USB 1.1 host controller (e.g. OHCI or UHCI). The Companion Host Controllers always manage Full- and Low-speed USB devices connected to the root ports. The CHCs have no knowledge of the high-speed-mode host controller. They can possibly be integrated into a USB 2.0 host controller with no modification.

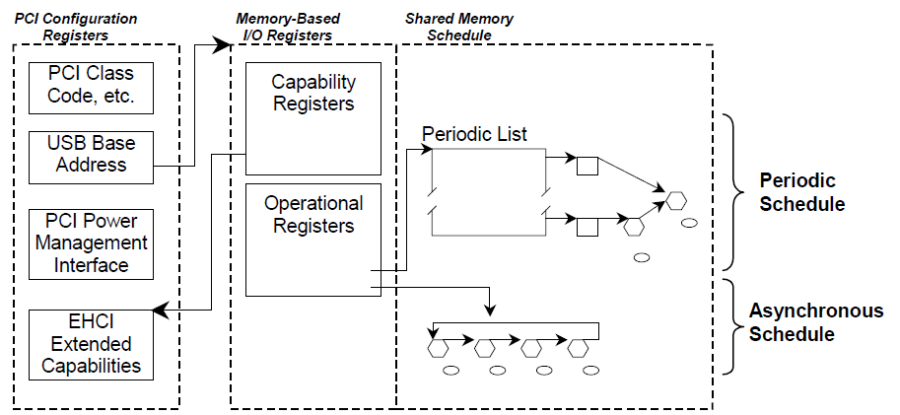

The EHCI interface defines three interface spaces:

- PCI Configuration Space: If the implementation includes PCI registers, they are used for system component enumeration and PCI power management.

- Register Space: Implementation-specific parameters and capabilities, plus operational control and status registers. This space, normally referred to as I/O space, must be implemented as memory-mapped I/O space.

- Schedule Interface Space: This is typically memory allocated and managed by the EHC Driver for the periodic and asynchronous schedules.

Figure 14-10 EHCI interface

14.3.3 OTG Controller

OTG driver used to control OTG controller work normally. OTG driver mainly maintain a OTG state machine and reflect platform USB state. When OTG is in the different OTG state, OTG driver will control OTG controller to do different things. For example, when OTG state become A-device, OTG driver configure registers to raise VBUS signal and control OTG controller to switch platform to USB host mode. When OTG state become B-device, OTG driver will configure registers to drop VBUS signal and control OTG controller to switch platform to USB device mode to wait host enumerate itself. And so on.

14.4 Data Transfer Types

There are four data transfer types defined in USB. Each type is optimized to match the service requirements between the client software and the USB device. The four types are:

- Control Transfers: Nonperiodic data transfers used to communicate configuration/command/status type information between client software and the USB device. It must be through Endpoint 0, and there can only be one device, and it must be supported. The maximum data size that can be transmitted at one time is 64 bytes and is bidirectional. Basically, when a USB device is plugged into the computer, the computer will ask for some information through Endpoint 0. According to the USB 2.0 specification, Host must reserve 10% of the bandwidth for Control transmission.

- Bulk Transfers: Nonperiodic data transfers used to communicate large amounts of information between client software and the USB device. The maximum size of data that can be transmitted at one time is 512 bytes (HS). It does not guarantee the bandwidth, it is usually HOST that the BUS has a bandwidth to choose to transmit Bulk data. In contrast, if the bandwidth is very idle, the amount of data that can be transmitted per second is large.

- Interrupt Transfers: Small data transfers used to communicate information from the USB device to the client software. The Host Controller Driver polls the USB device by issuing tokens to the device at a periodic interval sufficient for the requirements of the device. The maximum data size that can be transmitted at one time is 1024 bytes (HS), and it is transmitted periodically. The device side needs to declare how long this period is. In HS, it is in micro-second. It requires HOST to guarantee the bandwidth. If HOST cannot meet the bandwidth requirements of this device, HOST can refuse to start the device.

- Isochronous Transfers: Periodic data transfers with a constant data rate. Data transfers are correlated in time between the sender and receiver. It is very similar to Interrupt transmission, but it has no mechanism for error retransmission. All above three mode have a mechanism of error retransmission, and this mechanism is based on the premise that each transmission will have an ACK packet. Isochronous transmission does not require ACK packets, so it naturally can't detect errors.

In OHCI the data transfer types are classified into two categories: periodic and nonperiodic. Periodic transfers are interrupt and isochronous since they are scheduled to run at periodic intervals. Nonperiodic transfers are control and bulk since they are not scheduled to run at any

specific time, but rather on a time-available basis.

14.5 Data Structure

14.5.1 OHCI Data Structure

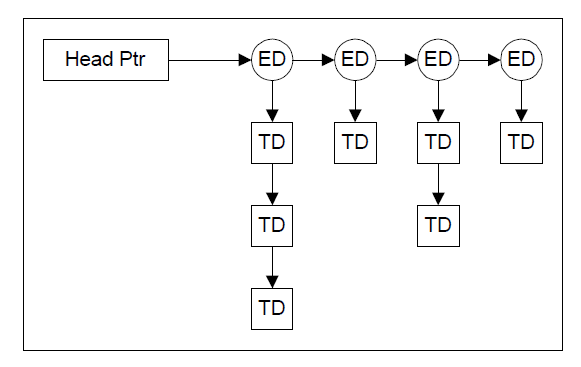

The basic building blocks for communication across the interface are the Endpoint Descriptor(ED) and Transfer Descriptor (TD). Each data transfer type has its own linked list of Endpoint Descriptors to be processed. Figure 14-10, Typical List Structure, is a representation of the data structure relationships.

Figure 14-11 OHCI data structure

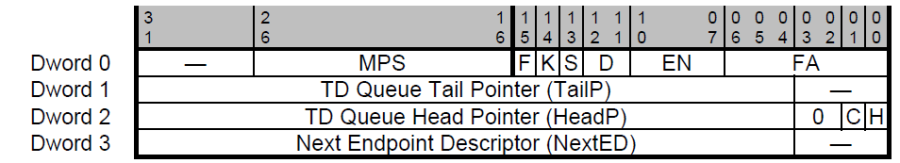

Endpoint Descriptors

The Host Controller Driver assigns an Endpoint Descriptor to each endpoint in the system. The Endpoint Descriptor contains the information necessary for the Host Controller to communicate with the endpoint. The fields include the maximum packet size, the endpoint address, the speed of the endpoint, and the direction of data flow. Endpoint Descriptors are linked in a list.

An Endpoint Descriptor (ED) is a 16-byte, memory resident structure that must be aligned to a 16-byte boundary. The Host Controller traverses lists of EDs and if there are TDs linked to an ED, the Host Controller performs the indicated transfer.

Figure 14-11 shows Endpoint Descriptor Format.

Figure 14-12 Endpoint Descriptor Format

Notes:

1. Fields containing '—' are not interpreted or modified by the Host Controller and are available for use by the Host Controller Driver for any purpose.

2. Fields containing '0' must be written to 0 by the Host Controller Driver before queued for Host Controller processing. If Host Controller has write access to the field, it will always write the field to 0.

Transfer Descriptors

A queue of Transfer Descriptors is linked to the Endpoint Descriptor for the specific endpoint. The Transfer Descriptor contains the information necessary to describe the data packets to be transferred. The fields include data toggle information, shared memory buffer location and completion status codes. Each Transfer Descriptor contains information that describes one or more data packets. The data buffer for each Transfer Descriptor ranges in size from 0 to 8192 bytes with a maximum of one physical page crossing. Transfer Descriptors are linked in a queue, the first one queued is the first one processed.

A Transfer Descriptor (TD) is a system memory data structure that is used by the Host Controller to define a buffer of data that will be moved to or from an endpoint. TDs come in two types: general and isochronous. The General TD is used for Interrupt, Control, and Bulk Endpoints and an Isochronous TD is used to deal with the unique requirements of isochronous transfers. Two TD types are supported because the nature of isochronous transfers does not lend itself to the standard DMA buffer format and the packetizing of the buffer required for isochronous transfers is too restrictive for general transfer types.

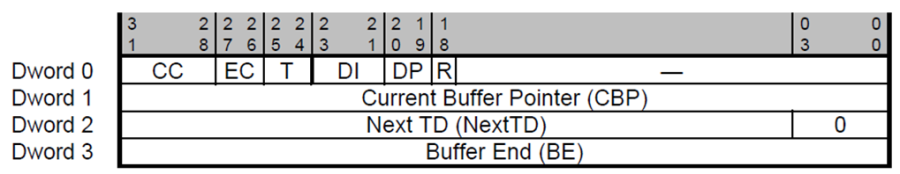

General Transfer Descriptor

Transfers for control, bulk, and interrupt all use the same format for their Transfer Descriptor (TD). This General TD is a 16-byte, host memory structure that must be aligned to a 16-byte boundary.

Figure 14-12 shows General Transfer Descriptor Format.

Figure 14-13 General Transfer Descriptor Format

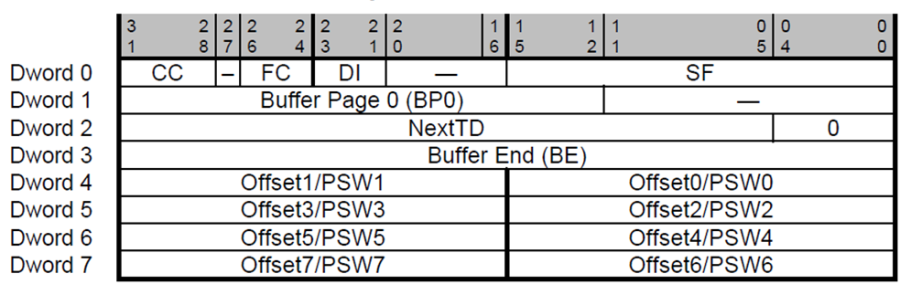

Isochronous Transfer Descriptor

An Isochronous TD is used exclusively for isochronous endpoints. All TDs linked to an ED with F = 1 must use this format. This 32-byte structure must be aligned to a 32-byte boundary in system memory.

Figure 14-13 shows General Transfer Descriptor Format.

Figure 14-14 Isochronous Transfer Descriptor Format

14.5.2 EHCI Data Structure

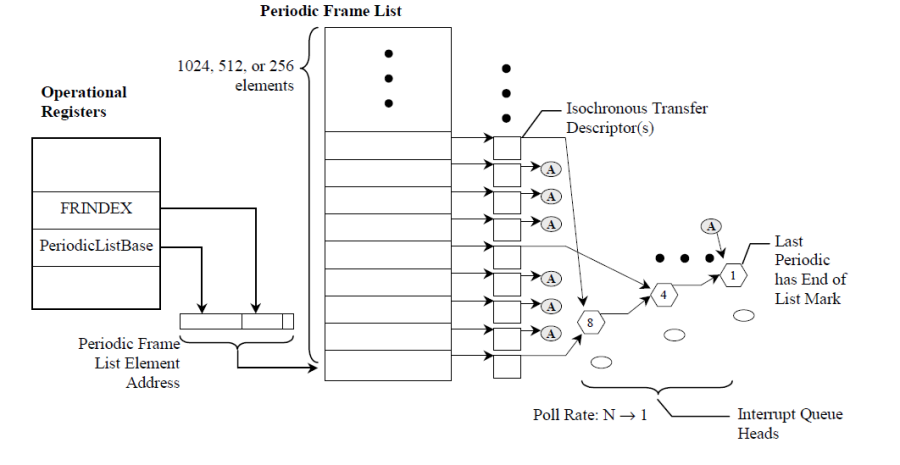

The data structure definitions in this chapter support a 32-bit memory buffer address space. The interface consists of a Periodic Schedule, Periodic Frame List, Asynchronous Schedule, Isochronous Transaction Descriptors, Split-transaction Isochronous Transfer Descriptors, Queue Heads and Queue Element Transfer Descriptors.

Periodic Frame List

This schedule is for all periodic transfers (isochronous and interrupt). The periodic schedule is referenced from the operational registers space using the PeriodicListBase address register and the FRINDEX register. The periodic schedule is based on an array of pointers called the Periodic Frame List. The PeriodicListBase address register is combined with the FRINDEX register to produce a memory pointer into the frame list. The Periodic Frame List implements a sliding window of work over time.

Figure 14-15 Periodic Frame List

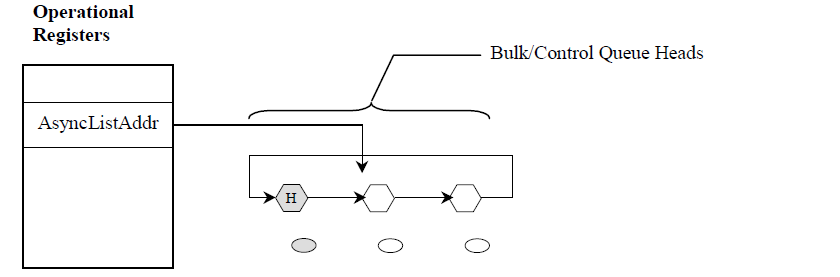

Asynchronous List Queue Head Pointer

The Asynchronous Transfer List (based at the AsyncListAddr register), is where all the control and bulk transfers are managed. Host controllers use this list only when it reaches the end of the periodic list, the periodic list is disabled, or the periodic list is empty.

Figure 14-16 Asynchronous Transfer List

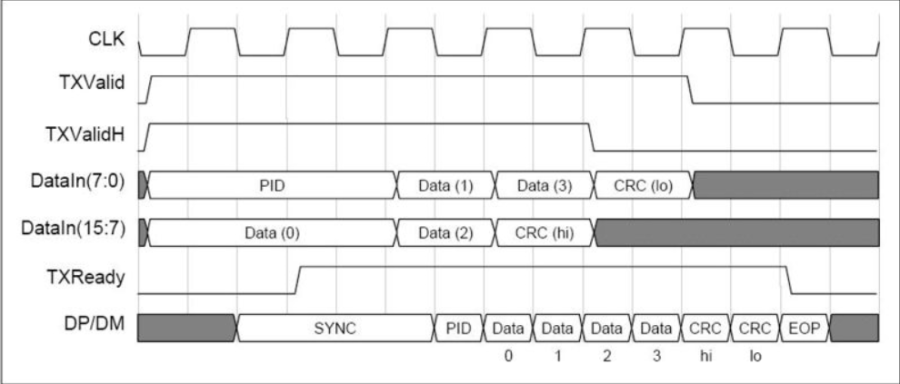

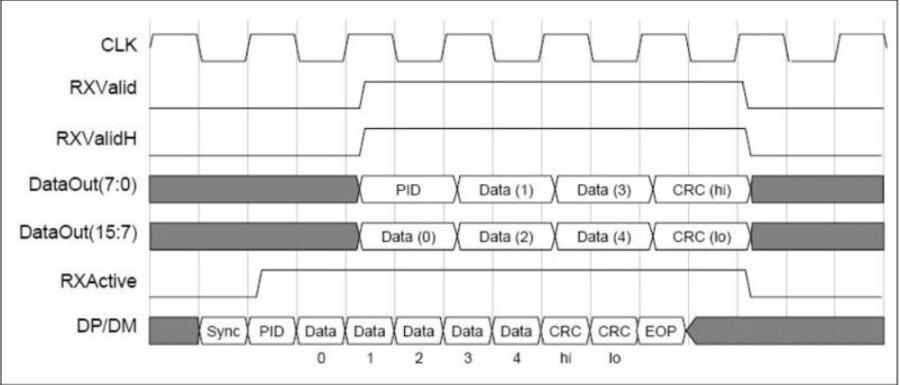

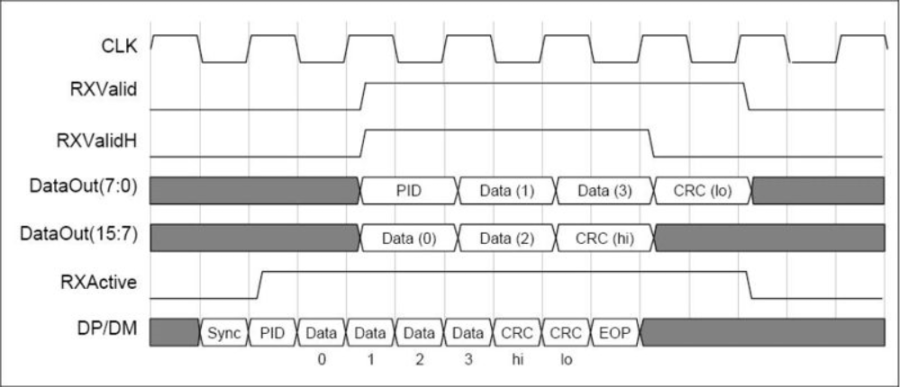

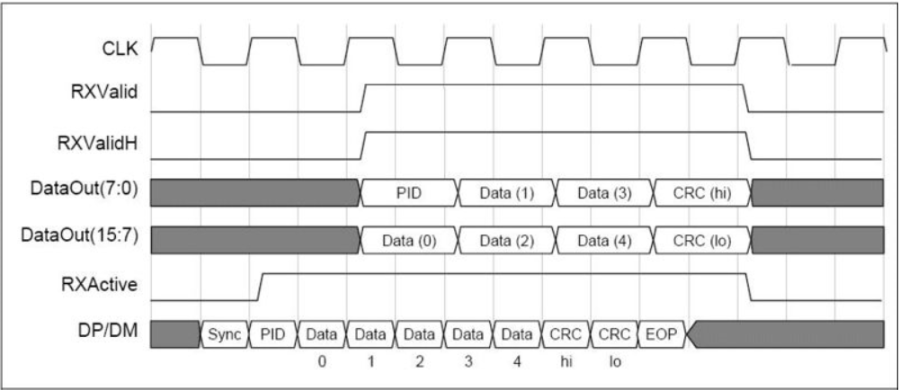

14.6 UTM Interface Timing Diagram

Figure 14-17 TX odd byte data

Figure 14-18 TX even byte data

Figure 14-19 RX odd byte data

Figure 14-20 RX even byte data

14.7 OHCI USB States

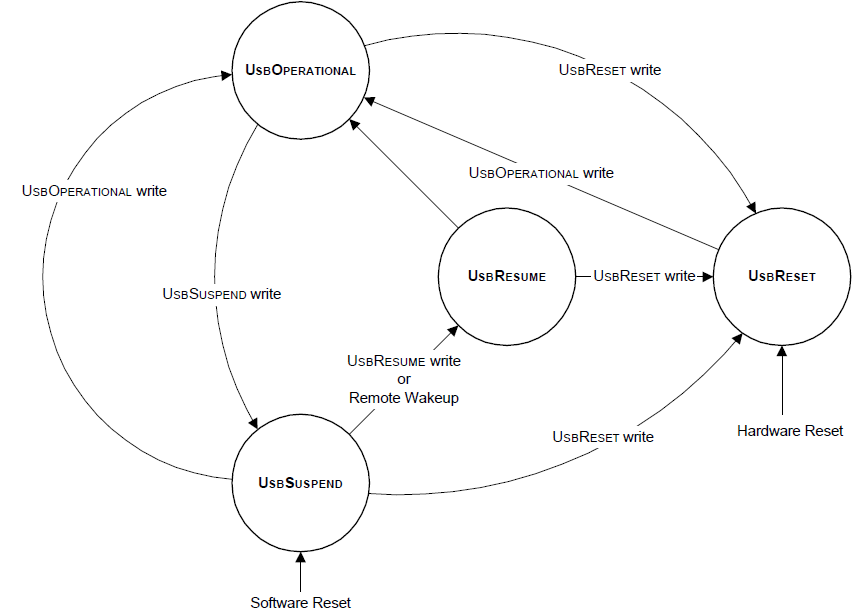

The Host Controller has four USB states visible to the Host Controller Driver via the Operational Registers: USBOPERATIONAL, USBRESET, USBSUSPEND, and USBRESUME. These states define the Host Controller responsibilities relating to USB signaling and bus states.

Figure 14-21 USB states

14.7.1 USBOPERATIONAL

When in the USBOPERATIONAL state, the Host Controller may process lists and will generate SOF Tokens. The USBOPERATIONAL state may be entered from the USBRESUME or USBRESET states. It may be exited to the USBRESET or USBSUSPEND states. When transitioning from USBRESET or USBRESUME to USBOPERATIONAL, the Host Controller is responsible for terminating the USB reset or resume signaling as defined in the USB Specification prior to sending a token.

14.7.2 USBRESET

When in the USBRESET state, the Host Controller forces reset signaling on the bus. The Host Controller's list processing and SOF Token generation are disabled while in USBRESET. The USBRESET state can be entered from any state at any time. The Host Controller defaults to the USBRESET state following a hardware reset. The Host Controller Driver is responsible for satisfying USB Reset signaling timing defined by the USB Specification.

14.7.3 USBSUSPEND

The USBSUSPEND state defines the USB Suspend state. The Host Controller's list processing and SOF Token generation are disabled. However, the Host Controller's remote wakeup logic must monitor USB wakeup activity. USBSUSPEND is entered following a software reset or from the USBOPERATIONAL state on command from the Host Controller Driver. While in USBSUSPEND, the Host Controller may force

a transition to the USBRESUME state due to a remote wakeup condition. This transition may conflict with the Host Controller Driver initiating a transition to the USBRESET state. If this situation occurs, the HCD-initiated transition to USBRESET has priority. The Host Controller Driver must wait 5 ms after transitioning to USBSUSPEND before transitioning to the USBRESUME state. Likewise, the Root Hub must wait 5 ms after the Host Controller enters USBSUSPEND before generating a local wakeup event and forcing a transition to USBRESUME. Following a software reset, the Host Controller Driver may cause a transition to USBOPERATIONAL if the transition occurs no more than 1 ms from the transition into USBSUSPEND. If the 1-ms period is violated, it is possible that devices on the bus will go into Suspend.

14.7.4 USBRESUME

When in the USBRESUME state, the Host Controller forces resume signaling on the bus. While in USBRESUME, the Root Hub is responsible for propagating the USB Resume signal to downstream ports as specified in the USB Specification. The Host Controller's list processing and SOF Token generation are disabled while in USBRESUME. USBRESUME is only entered from USBSUSPEND. The transition to USBRESUME can be initiated by the Host Controller Driver or by a USB remote wakeup signaled by the Root Hub. The Host

Controller is responsible for resolving state transition conflicts between the hardware wakeup and Host Controller Driver initiated state transitions. Legal state transitions from USBRESUME are to USBRESET and to USBOPERATIONAL. The Host Controller Driver is responsible for USB Resume signal timing as defined by the USB Specification.

14.8 USB OPERATION

14.8.1 OHCI Initialization

Initialize the open host controller, software should perform the following steps:

- Set software reset in Group1.1 UHO_HcControl register bit[7:6]=0.

- Configure OHCI command in Group1.1 UHO_HcControl register.

- Select routed all ports to OHCI by set 0 to bit0 of Group2.24 UHE_CONFIGFLAG register.

Note: Due to some devices on the USB that may take a long time to reset, it is desirable that the Host Controller Driver startup process not transition to the USBRESET state if possible.

14.8.2 EHCI Initialization

In order to initialize the enhanced host controller, software should perform the following steps:

- Set software reset in Group2.8 UHE_USBCMD register bit[1]=1.

- Program the Group2.12 UHE_CTRLDESSEGMENT register with 4-Gigabyte segment where all of the interface data structures are allocated.

- Write the appropriate value to the Group2.10 UHE_USBINTR register to enable the appropriate interrupts.

- Write the base address of the Periodic Frame List to the Group2.13 UHE_PERIODICLISTBASE register. Write the base address of the Asynchronous Frame List to the Group2.14 UHE_ASYNCLISTBASE register.

- Enable Periodic schedule in Gruop2.8 UHE_USBCMD register bit4, enable Asynchronous schedule in Gruop2.8 UHE_USBCMD register bit5.

- Write the Group2.8 UHE_USBCMD register to set the desired interrupt threshold, frame list size (if applicable).

- Write 1 to bit0 of Group2.24 UHE_CONFIGFLAG register to route all ports to the EHCI controller.

- Wait device connect by check Group2.25 UHE_PORTSC register bit0=1.

- Issue port reset by set Group2.25 UHE_PORTSC register bit8=1.

- Turn the host controller ON via setting the Run/Stop bit in Gruop2.8 UHE_USBCMD register bit0.

14.8.3 OTG Initialization

- Select work mode in Group8.0 MODE_SELECT register bit[1:0]. Default as 0 with OTG2.0.

- Confirm work role by read Group8.0 MODE_SELECT register bit[1:0] after "ID_CHANGE_IF" interrupt is assert. The ID_CHANGE_IF flag is in Group8.3 OTG_ST register bit1.

- Depend on work mode, set initial of OTG CTRL in Group8.1 OTG_DEVICE_CTRL register. Set SRP/ADP_SUPPORT in Group8.0 MODE_SELECT bit2 and bit3

- Set SRP/HNP/ADP related timers in Group8.4~8.29 registers.

14.9 Pattern of come to USB2.0

Define the line state J, K, SE0 of USB, that is, D+, D-, as shown in the following table.

J | K | SE0 | |

D+ | 1 | 0 | 0 |

D- | 0 | 1 | 0 |

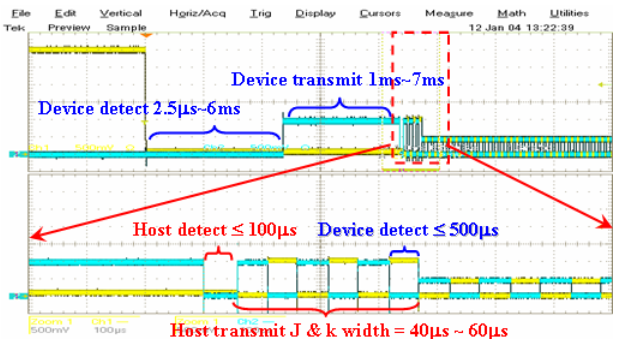

USB 2.0 is made under the existing architecture that does not destroy USB1.1. Unless host and device are both 2.0, they are all transmitted with 1.1. The method of recognition is chirp, which is described as follows. The yellow line is D+ and the blue line is D-. The timing is as follows:

Figure 14-22 USB2.0 chirp pattern

- D+ pull up to 3.3V after device plug in

- Host drive bus reset (se0, both D+,D- = 0)

- Device chirp K 1ms-7ms. (D- = 800mV)

- Host chirp KJKJKJ sequence pattern

- Device recognizes 6 groups of kj and enters USB2.0 mode, turn on 45 Ohm pull down to GND at the same time, it make 800mV level become 400mV.

14.10 USB Interrupts

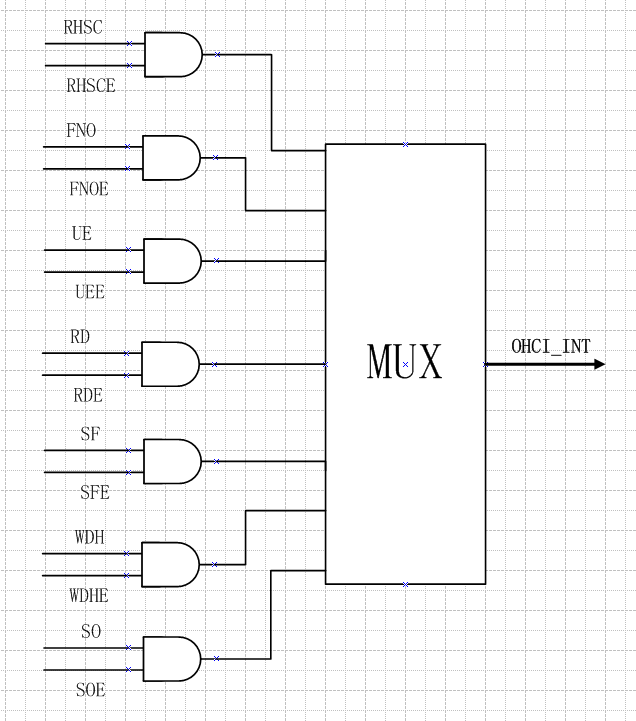

14.10.1 OHCI Interrupts

OHCI interrupt is from OHCI block with level signals. The detail interrupt information refer to the USBC0 Group1.3 bit[6:0] UHO_HcInterruptStatus Register. The enable register is USBC0 Group1.4 bit[6:0] UHO_HcInterruptEnable. Figure 14-23 shows the OHCI interrupt tree.

Figure 14-23 OHCI interrupt tree

- RHSC: Root Hub content change status bit

- FNO: Frame number overflow status bit

- UE: Un-recoverable error

- RD: Resume signaling detected status bit

- SF: Each start of a frame status bit

- WDH: HC has written HcDoneHead to HccaDoneHead status bit

- SO: USB schedule for the current Frame overruns status bit

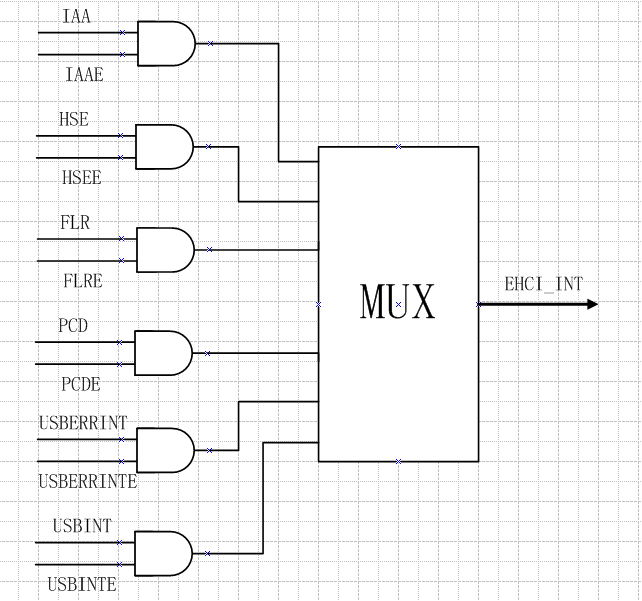

14.10.2 EHCI Interrupts

EHCI interrupt is from EHCI block with level signals. The detail interrupt information refer to the USBC0 Group2.9 bit[5:0] UHE_USBSTS register. The enable register is USBC0 Group2.10 bit[5:0] UHE_USBINTR. Figure 14-24 shows the EHCI interrupt tree.

Figure 14-24 EHCI interrupt tree

- IAA: Indicates the assertion of Async Advance interrupt

- HSE: Host system error

- FLR: Indicate the Frame List Index rolls over from its maximum value to zero

- PCD: Indicate any port of the port owner bit is set to zero or from zero to a one

- USBERRINT: Indicate completion of a USB transaction results in an error condition

- USBINT: Indicate the completion of a USB transaction

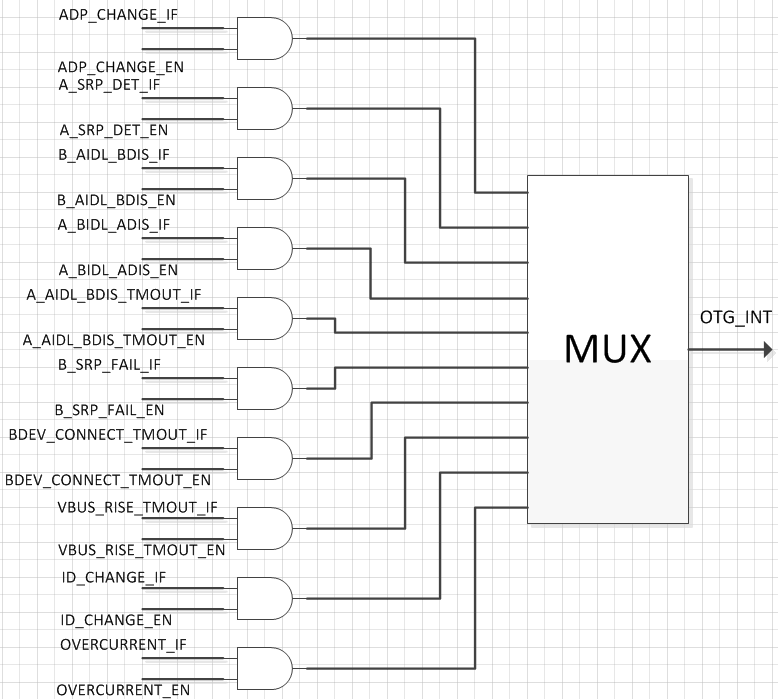

14.10.3 OTG Interrupts

The detail OTG interrupt information refer to the USBC0 Group8.3 bit[9:0] OTG_ST register. The enable register is USBC0 Group8.2 bit[9:0] OTG_INT_EN. Figure 14-25 shows the OTG interrupt tree.

Figure 14-25 OTG interrupt tree

- ADP_CHANGE_IF: Indicate the ADP changed

- A_SRP_DET_IF: Indicate A-device(Host side) have detected SRP

- B_AIDL_BDIS_IF: Indicate B-device(Device side) disconnects to A-device(Host side) to start HNP

- A_BIDL_ADIS_IF: Indicate A-device(Host side) disconnects to B-device(Device side) to start HNP

- A_AIDL_BDIS_TMOUT_IF: Waiting for a disconnect timeout when HNP

- B_SRP_FAIL_IF: B-device SRP fail

- BDEV_CONNECT_TMOUT_IF: A-device waits B-device connect timeout

- VBUS_RISE_TMOUT_IF: A-device waits vbus valid timeout

- ID_CHANGE_IF: ID pin has changed

- OVERCURRENT_IF: An attached B-device draws more current

14.11 Registers Map

14.11.1 Registers Memory Map

Memory Map Start Address | Data Width | Group No. | Module |

|---|---|---|---|

0x9C004A80 | 32 | 149 | UPHY0 (USB PHY 0) |

0x9C004B00 | 32 | 150 | UPHY1 (USB PHY1) |

Table 14-1 USB PHY registers group list of RGST table

Both USB PHY registers have the same offset in corresponding register group. Only USB PHY0 (UPHY0) registers are described in following register description, for USB PHY1 please refer to UPHY0 description for more detail.

Memory Map Start Address | Data Width | Group No. | Module |

|---|---|---|---|

0x9C102000 | 32 | USBC0 Group 0 | USB0 HOST |

0x9C102080 | 32 | USBC0 Group 1 | USB0 OHCI |

0x9C102100 | 32 | USBC0 Group 2 | USB0 EHCI |

0x9C102400 | 32 | USBC0 Group 8 | USB0 OTG |

0x9C102800 | 32 | USBC0 Group 16 | USB0 DMA |

0x9C102880 | 32 | USBC0 Group 17 | USB0 INTERRUPT |

0x9C102900 | 32 | USBC0 Group 18 | USB0 EP0~4 |

0x9C102980 | 32 | USBC0 Group 19 | USB0 EP5/6/7 |

0x9C102A00 | 32 | USBC0 Group 20 | USB0 EP8/9/A/B |

0x9C102A80 | 32 | USBC0 Group 21 | USB0 EPC/D |

0x9C102B00 | 32 | USBC0 Group 22 | USB0 Phyclk Domain Interrupt |

0x9C102B80 | 32 | USBC0 Group 23 | USB0 Bulk Out FIFO |

0x9C103000 | 32 | USBC1 Group 0 | USB1 HOST |

0x9C103080 | 32 | USBC1 Group 1 | USB1 OHCI |

0x9C103100 | 32 | USBC1 Group 2 | USB1 EHCI |

0x9C103400 | 32 | USBC1 Group 8 | USB1 OTG |

0x9C103800 | 32 | USBC1 Group 16 | USB1 DMA |

0x9C103880 | 32 | USBC1 Group 17 | USB1 INTERRUPT |

0x9C103900 | 32 | USBC1 Group 18 | USB1 EP0~4 |

0x9C103980 | 32 | USBC1 Group 19 | USB1 EP5/6/7 |

0x9C103A00 | 32 | USBC1 Group 20 | USB1 EP8/9/A/B |

0x9C103A80 | 32 | USBC1 Group 21 | USB1 EPC/D |

0x9C103B00 | 32 | USBC1 Group 22 | USB1 Phyclk Domain Interrupt |

0x9C103B80 | 32 | USBC1 Group 23 | USB1 Bulk Out FIFO |

Table 14-2 USB control registers group list of AMBA table

Only USB0 relative register group will be described in register description, for USB1, please refer to USB0 corresponding group description for more detail

14.11.2 Registers Description

RGST Table Group 149 UPHY0

149.0 CONFIG0 (cfg0)

Address: 0x9C004A80

Reset: 0x0000 0080

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| J WAKE SEL | 7:5 | RW | J WAKE SEL controls wake up time. 0x0 : 0.54ms ˜ 1.09ms 0x1 : 1.09ms ˜ 1.68ms 0x2 : 1.68ms ˜ 2.18ms 0x3 : 2.18ms ˜ 2.73ms 0x4 : 2.73ms ˜ 3.27ms(default) 0x5 : 3.27ms ˜ 3.82ms 0x6 : 4.36ms ˜ 4.91ms 0x7 : 4.91ms ˜ 5.46ms |

| J ANG LB | 4 | RW | Analog Loopback mode. 0x0 : turn off analog loopback(default). 0x1 : turn on analog loopback. |

| J DIG LB | 3 | RW | Digital Loopback mode. 0x0 : turn off digital loopback(default). 0x1 : turn on digital loopback. |

J IPX2 | 2 | RW | Charge Pump Current Option. |

J ENABLE CNTR | 1 | RW | Bist mode counter enable of succcess and fail. |

J CLEAR CNTR | 0 | RW | Bist mode counter clear of succcess and fail. |

149.1 CONFIG1 (cfg1)

Address: 0x9C004A84

Reset: 0x0000 0021

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| J HS TX DELAY | 7:6 | RW | Fine tune TX Delay 0x0 : No delay(default). 0x1 : Delay 1 clock. 0x2 : Delay 2 clock. 0x3 : No delay. |

| J HS TX PWRSAV | 5 | RW | High Speed TX power saving. When this item actives, it means TX driver will turn on with TXValid. When this item is low, it means TX driver will always turn on. |

| J HS RX DROP2 | 4 | RW | Set the EOP receive condition sensitive If DEV_DET fall very quickly, this may cause some valid EOP bit lose and cause correct packet become RXERROR, so this register set medium EOP detection. 0x0: do nothing(default) |

| J HS RX DROP4 | 3 | RW | Set the EOP receive condition very sensitive If DEV_DET fall very quickly, this may cause some valid EOP bit lose and cause correct packet become RXERROR, so this register set very sensitive EOP detection. 0: do nothing(default) |

| J HS RX LPFIL | 2:1 | RW | CDR data channel phase shift precision 0x0: shift precision is very high 0x1: shift precision is high 0x2: shift precision is medium 0x3: shift precision is slow |

| J FS TX PREDR IDLE | 0 | RW | For 1st cross over point perfection 0: Disable(default) 1 : Enable |

149.2 CONFIG2 (cfg2)

Address: 0x9C004A88

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| J DPN | 7:4 | RW | DP Full speed falling time select. The larger the value, the shorter the DP falling transition time. Default: 4'b0000 |

| J DPP | 3:0 | RW | DP Full speed rising time select. The larger the value, the shorter the DP rising transition time. Default: 4'b0000 |

149.3 CONFIG3 (cfg3)

Address: 0x9C004A8C

Reset: 0x0000 0021

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | RESERVED |

J FORCE PU2 HI | 7 | RW | J FORCE PU2 HI |

J FORCE PU2 LO | 6 | RW | J FORCE PU2 LO |

J FORCE DISC ON | 5 | RW | Whenever DPDM PULLDOWN, the system force into chirp mode |

| DEBUG_INT | 4:0 | RW | Reserved for internal debug purpose. Access to this register may cause unexpected malfunction |

149.4 CONFIG4 (cfg4)

Address: 0x9C004A90

Reset: 0x0000 0020

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| J IPX3 | 7 | RW | Charge Pump Current Option. macro spec. |

| J IPX1 | 6 | RW | Charge Pump Current Option. macro spec. |

J SKIP NOXTION | 5 | RW | J SKIP NOXTION |

J PGMODE | 4:0 | RW | Pattern Selection of bist test |

149.5 CONFIG5 (cfg5)

Address: 0x9C004A94

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | RESERVED |

SUCC CNTR | 7:4 | RU | Bit mode success counter When successive 15 packages success, BIST test success and done. |

FAIL CNTR | 3:0 | RU | Bit mode fail counter When successive 15 packages fail, BIST test fail and done. |

149.6 CONFIG6 (cfg6)

Address: 0x9C004A98

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| J DMN | 7:4 | RW | DM Full speed falling time select. The larger the value, the shorter the DP falling transition time. Default: 4'b0000 |

| J DMP | 3:0 | RW | DM Full speed rising time select. The larger the value, the shorter the DP rising transition time. Default: 4'b0000 |

149.7 CONFIG7 (cfg7)

Address: 0x9C004A9C

Reset: 0x0000 008A

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| J EN INR | 7 | RW | Internal Rext function enable 0x0 : disable 0x1 : enable(default) |

| J R TRIM | 6:5 | RW | Loop filter R trim table {R TRIM1,R TRIM0} 0x0 : 80K 0x1 : 18K 0x2 : 16K 0x3 : 14K |

| J DISC | 4:0 | RW | control disconnect voltage(16.5mV/step) 0x00 : value 405mv. 0x0a : value 570mv(default). 0x1e : 900mv. 0x1f : Disable Disconnection |

149.8 CONFIG8 (cfg8)

Address: 0x9C004AA0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | RESERVED |

J FS TX J DELAY | 7:6 | RW | Full speed DP delay cycle |

J FS TX K DELAY | 5:4 | RW | Full speed DM delay cycle |

J LS TX J DELAY | 3:2 | RW | Low speed DP delay cycle |

J LS TX K DELAY | 1:0 | RW | Low speed DM delay cycle |

149.9 CONFIG9 (cfg9)

Address: 0x9C004AA4

Reset: 0x0000 0006

| Field Name | Bit | Access | Description |

| Reserved | 31:5 | RO | RESERVED |

| J FL FORCE FS | 4 | RW | Enable Config device error state 0 : enable error state(default) |

| J FL DP PILLUP | 3 | RW | Config device DP or MP resister pullup 0 : Full-low speed DP pull up(default) |

| J FL SAMPLE SEL | 2 | RW | Enable Full-low speed rx linestat sample circuit 0 : disable Full-low speed rx linestat sample circuit |

| J DIS FSM WAIT4MS EN | 1 | RW | Disable HOSTDISC error state 0 : enable error state 1 : disable error state(default) |

| J FS ONLY | 0 | RW | Disable UPHY AFE Low speed circuit at Low speed 0 : Low speed circuit use in Low speed(default) 1 : Full speed circuit usb in Low speed |

149.10 CONFIG10 (cfg10)

Address: 0x9C004AA8

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| NA | 7 | RO | High speed disconnect signal with filter. 0 : disconnect is not happened(default) 1 : disconnect is happened |

J HSDISC LPFILTER | 6:4 | RW | High speed disconnect filter number |

J ALDISC OFF | 3 | RW | Host disconnect force 0 |

J ALDISC ON | 2 | RW | Host disconnect force 1 |

J HSDISC OFF | 1 | RW | High speed disconnect force 0 |

J HSDISC ON | 0 | RW | High speed disconnect force 1 |

149.11 CONFIG11 (cfg11)

Address: 0x9C004AAC

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| LINESTATE | 7:6 | RO | Linestate signal without control 0x0 : SE0 state(default). 0x1 : J state. 0x2 : K state. 0x3 : SE1 state. |

| Reserved | 5:3 | RO | RESERVED |

| J LINE EN | 2 | RW | Force Linestate signal 0 : disable force linestate(default). 1 : force linestate. |

| J LINE DATA | 1:0 | RW | Force Linestate signal value 0x0 : SE0 state(default). 0x1 : J state. 0x2 : K state. 0x3 : SE1 state. |

149.12 CONFIG12 (cfg12)

Address: 0x9C004AB0

Reset: 0x0000 0007

| Field Name | Bit | Access | Description |

| Reserved | 31:0 | RO | Reserved for Industrial Debug Purpose |

149.13 CONFIG13 (cfg13)

Address: 0x9C004AB4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

DEBUG_INT | 31:0 | RU | Reserved for Industrial Debug Purpose |

149.14 CONFIG14 (cfg14)

Address: 0x9C004AB8

Reset: 0x0000 0011

| Field Name | Bit | Access | Description |

| Reserved | 31:5 | RO | RESERVED |

PHY R CONFIG | 4 | RW | UPHY resume config mode |

FS/LS RX DCP | 3:2 | RW | FS/LS RX data capture point |

FS/LS RX SCP | 1:0 | RW | FS/LS RX SYNC capture point |

149.15 CONFIG15 (cfg15)

Address: 0x9C004ABC

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:2 | RO | RESERVED |

| HS DIS DG FLT | 1:0 | RW | High speed disconnect de-glitch filter 0x0 : no de-glitch(default). 0x1 : 1 time de-glitch. 0x2 : 2 time de-glitch. 0x3 : NA |

149.16 CONFIG16 (cfg16)

Address: 0x9C004AC0

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

J FORCE VDM SRC | 7 | RW | FORCE DM voltage. |

J TBCWAIT[1:0] | 6:5 | RW | Battery charger disconnect to rework time. |

J TVDM SRC DIS[1:0] | 4:3 | RW | J Battery charger polling DP high to send dm voltage time. |

J TVDM SRC EN[1:0] | 2:1 | RW | Battery charger polling DP low to disable dm voltage time. |

J BC ENABLE | 0 | RW | Battery Charger CDP Function Enable. |

149.17 CONFIG17 (cfg17)

Address: 0x9C004AC4

Reset: 0x0000 0092

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

IBG TRIM0[2:0] | 7:5 | RW | Current of current source in CDP mode. 0x0f : TTNVNT (default) I=100uA 0x12 : FFHVLT 0x0a : FFHVHT 0x17 : SSHVLT 0x0c : SSLVHT 0x17 : SSLVLT |

J VDATREF TRIM[3:0] | 4:1 | RW | Reference voltage of comparator in CDP mode. VDATREF TRIM[3:0] 0x1 : 250mv 0x2 : 300mv 0x4 : 350mv 0x8 : 400mv 0x9 : default |

J EN DCP | 0 | RW | Battery Charger DCP Function Enable. 0 : disable DCP(default) 1 : enable DCP |

149.18 CONFIG18 (cfg18)

Address: 0x9C004AC8

Reset: 0x0000 0010

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| BC DETECT STATUS | 7 | RW | Indicate Battery Charge handshake status 0:BC handshake done(default), 1:BC handshake is in progress. |

| VDMSRC TRIM[4:0] | 6:2 | RW | Dm source voltage. 0x01 : 500mv 0x02 : 550mv 0x04 : 600mv(default) 0x08 : 650mv 0x10 : 700mv |

| IBG TRIM1[1:0] | 1:0 | RW | Current of current source in CDP mode. 0x0f : TTNVNT (default) I=100uA 0x12 : FFHVLT 0x0a : FFHVHT 0x17 : SSHVLT 0x0c : SSLVHT 0x17 : SSLVLT |

149.19 CONFIG19 (cfg19)

Address: 0x9C004ACC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserved | 31:1 | RO | RESERVED |

EN HSRXACTIVE INT | 0 | RW | Enable UPHY Interrupt. |

149.20 CONFIG20 (cfg20)

Address: 0x9C004AD0

Reset: 0x0000 0009

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

Reserved | 7 | RW | RESERVED |

Reserved | 6 | RW | RESERVED |

NA | 5:0 | RW | NA |

J AC2 0 B | 5:3 | RW | OTG Discharge Current Option. 0x0: 5uA 0x1: 10uA 0x2: 15uA 0x3: 20uA 0x4: 30uA (default) 0x5: 40uA 0x6: 50uA 0x7: 60uA |

J AC2 0 | 2:0 | RW | OTG Charge Current Option. 0x0: 5uA 0x1: 10uA 0x2: 15uA 0x3: 20uA 0x4: 30uA (default) 0x5: 40uA 0x6: 50uA 0x7: 60uA |

149.21 CONFIG21 (cfg21)

Address: 0x9C004AD4

Reset: 0x0000 0001

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | RESERVED |

BC DETECT STS | 7 | RO | Battery Charge is in detect progress. |

BC PRTBL STS | 6 | RO | Battery Charge successful detect PRTBL STS. |

BC VDMSRC STS | 5 | RO | Battery Charge successful send VDM SRC. |

BC DISC CNT | 4:3 | RO | Battery Charge detect disconnect counter. |

BC SUCC CNT | 2:1 | RO | Battery Charge handshake successful counter. |

J BC SUSPEND EN | 0 | RW | Enable Battery Charge handshake while PHY in SUSPEND MODE. |

149.22 CONFIG22 (cfg22)

Address: 0x9C004AD8

Reset: 0x0000 0077

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | RESERVED |

DCP2P7V | 7:4 | RW | Battery Charge DCP 2.7V control to APHY DCP 1.2V mode dm source voltage trimming: triming step=25mV 0x0: 1.025V 0x3: 1.1V 0x7: 1.2V 0xb: 1.3V 0xe: 1.4V |

DCP1P2V | 3:0 | RW | Battery Charge DCP 1.2V control to APHY DCP 2.7V mode dm source voltage trimming: triming step=25mV 0x0: 2.525V 0x3: 2.6V 0x7: 2.7V 0xb: 2.8V 0xe: 2.9V |

149.23 CONFIG23 (cfg23)

Address: 0x9C004ADC

Reset: 0x0000 0018

| Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | RESERVED |

RFU | 7:6 | RW | Reserved for future use |

PROB | 5:3 | RW | APHY Probe control 0x0: 597.5mV 0x1: 617.5mV 0x2: 636.5mV 0x3: 656.5mV (default) 0x4: 675.5mV 0x5: 695.5mV 0x6: 714.5mV 0x7: 734.5mV |

R TEST TIEH | 2 | RW | R TEST Tie High control to APHY 0: disable (default) 1: USB_R_TEST=AVDDC33 |

EN DCP2P7V | 1 | RW | Enable 2.7V DCP mode 0: disable 2.7V DCP mode (default) 1: enable 2.7V DCP mode |

EN DCP1P2V | 0 | RW | Enable 1.2V DCP mode 0: disable 1.2V DCP mode (default) 1: enable 1.2V DCP mode |

149.24 CONFIG24 (cfg24)

Address: 0x9C004AE0

Reset: 0x0000 0001

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| BC AUTO RST | 7 | RW | Battery Charge auto re-start enable 1'b0: Disable auto re-start. 1'b1: Enable auto re-start(Default) |

| TBC AUTO RST | 6:0 | RW | Battery Charge auto re-start timer When counter equal to J_TBC_AUTO_RST, internal FSM timeout. Real time is 606ms*J_TBC_AUTO_RST |

149.25 CONFIG25 (cfg25)

Address: 0x9C004AE4

Reset: 0x0000 0004

| Field Name | Bit | Access | Description |

| Reserved | 31:8 | RO | RESERVED |

| RFU | 7:3 | RW | Reserved for future use |

| SQ CT | 2:0 | RW | RX Squelch level control to APHY 0x0: 67.8mV 0x1: 84.5mV 0x2: 101.2mV 0x3: 118.1mV 0x4: 135.0mV (default) 0x5: 152.1mV 0x6: 169.2mV 0x7: 186.6mV |

USB Controller System 0 (USBC0)

Group 0 USB Host Control (UHC)

0.0 USB Host Version (UHVERSION)

Address: 0x9C102000

Reset: 0xC2120101

| Field Name | Bit | Access | Description |

| UHVERSION | 31:0 | RO | USB Host Hardware Version Read as '0xC2120101' |

0.4 USB Power Control and Status (UHPOWERCS PORT)

Address: 0x9C102010

Reset: 0x00070000

| Field Name | Bit | Access | Description |

reserved | 31:19 | RO | RESERVED |

UPHY SUSPENDM | 18 | RO | UPHY Suspend Signal |

UPHY PARTIALM | 17 | RO | UPHY Partial Signal |

USB CLK EN | 16 | RO | USB Clock Enable |

reserved | 15:12 | RO | RESERVED |

UPHY PAR EN | 11 | RW | UPHY Partial Enable |

UPHY SUSP EN | 10 | RW | UPHY Suspend Enable |

UPHY PAR CTRL | 9 | RW | UPHY Partial Control |

UPHY SUSP CTRL | 8 | RW | UPHY Suspend Control |

reserved | 7:2 | RO | RESERVED |

USBCLK SEL | 1 | RW | USB Clock Domain Clock Select |

reserved | 0 | RO | RESERVED |

Group 1 USB Host OHCI Controller

1.0 OHCI HcRevision Register (UHO HcRevision)

Address: 0x9C102080

Reset: 0x00000010

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | Reserved |

REV | 7:0 | RO | OHCI Revision |

1.1 OHCI HcControl Register (UHO HcControl)

Address: 0x9C102084

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| Reserved | 31:11 | RO | Reserved |

| RWE | 10 | RO | RemoteWakeupEnable This bit is used by HCD to enable or disable the remote wakeup signaling upon the detection of upstream resume. read as '0' |

| RWC | 9 | RO | RemoteWakeupConnected This bit indicates whether HC supports remote wakeup signaling, read as '0' |

| IR | 8 | RW | InterruptRouting Not support. |

| HCFS | 7:6 | RW | HostControllerFunctionalState for USB 0x0 : USBRESET (default) 0x1 : USBRESUME 0x2 : USBOPERATIONAL 0x3 : USBSUSPEND |

| BLE | 5 | RW | BulkListEnable Enable or disable the processing of the Bulk list in the next frame. Default disabled |

CLE | 4 | RW | ControlListEnable |

IE | 3 | RW | IsochronousEnable |

PLE | 2 | RW | PeriodicListEnable |

CBSR | 1:0 | RW | ControlBulkServiceRatio |

1.2 OHCI HcCommandStatus Register (UHO HcCommandStatus)

Address: 0x9C102088

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| Reserved | 31:18 | RO | Reserved |

| SOC | 17:16 | RO | SchedulingOverrunCount Used by HCD to monitor any persistent scheduling problems. |

| Reserved | 15:4 | RO | Reserved |

| OCR | 3 | RO | OwnershipChangeRequest Not support |

| BLF | 2 | RW | BulkListFilled Indicate whether there are any TDs on the Bulk list. 1: There is TDs on the Bulk list. 0: There is no TDs on the Bulk list (default) |

| CLF | 1 | RW | ControlListFilled Indicate whether there are any TDs on the Control list. 1: There is TDs on the Control list. 0: There is no TDs on the Control list (default |

| HCR | 0 | other | HostControllerReset Write 1, host Controller software reset, then clear this field by itself. |

1.3 OHCI HcInterruptStatus Register (UHO HcInterruptStatus)

Address: 0x9C10208C

Reset: 0x00000000

Field Name | Bit | Access | Description |

Reserved | 31 | RO | Reserved |

OC | 30 | RO | OwnershipChange |

Reserved | 29:7 | RO | Reserved |

RHSC | 6 | RWC | RootHubStatusChange |

FNO | 5 | RWC | FrameNumberOverflow |

UE | 4 | RWC | UnrecoverableError |

RD | 3 | RWC | ResumeDetected |

SF | 2 | RWC | StartofFrame |

WDH | 1 | RWC | WritebackDoneHead |

SO | 0 | RWC | SchedulingOverrun |

1.4 OHCI HcInterruptEnable Register (UHO HcInterruptEnable)

Address: 0x9C102090

Reset: 0x00000000

Field Name | Bit | Access | Description |

MIE | 31 | Other | MasterInterruptEnable |

OC | 30 | RO | OwnershipChange |

Reserved | 29:7 | RO | Reserved |

RHSC | 6 | Other | RootHubStatusChange |

FNO | 5 | Other | FrameNumberOverflow |

UE | 4 | Other | UnrecoverableError |

RD | 3 | Other | ResumeDetected |

SF | 2 | Other | StartofFrame |

WDH | 1 | Other | WritebackDoneHead |

SO | 0 | Other | SchedulingOverrun |

1.5 OHCI HcInterruptDisable Register (UHO HcInterruptDisable)

Address: 0x9C102094

Reset: 0x00000000

Field Name | Bit | Access | Description |

MIE | 31 | Other | MasterInterruptEnable |

OC | 30 | RO | OwnershipChange |

Reserved | 29:7 | RO | Reserved |

RHSC | 6 | Other | RootHubStatusChange |

FNO | 5 | Other | FrameNumberOverflow |

UE | 4 | Other | UnrecoverableError |

RD | 3 | Other | ResumeDetected |

SF | 2 | Other | StartofFrame |

WDH | 1 | Other | WritebackDoneHead |

SO | 0 | Other | SchedulingOverrun |

1.6 OHCI HcHCCA Register (UHO HcHCCA)

Address: 0x9C102098

Reset: 0x00000000

Field Name | Bit | Access | Description |

HCCA | 31:8 | RW | Host Controller Communication Area |

Reserved | 7:0 | RO | Reserved |

1.7 OHCI HcPeriodCurrentED Register (UHO HcPeriodCurrentED)

Address: 0x9C10209C

Reset: 0x00000000

Field Name | Bit | Access | Description |

PCED | 31:4 | RO | PeriodCurrentED |

Reserved | 3:0 | RO | Reserved |

1.8 OHCI HcControlHeadED Register (UHO HcControlHeadED)

Address: 0x9C1020A0

Reset: 0x00000000

Field Name | Bit | Access | Description |

CHED | 31:4 | RW | ControlHeadED |

Reserved | 3:0 | RO | Reserved |

1.9 OHCI HcControlCurrentED Register (UHO HcControlCurrentED)

Address: 0x9C1020A4

Reset: 0x00000000

Field Name | Bit | Access | Description |

CCED | 31:4 | RW | ControlCurrentED |

Reserved | 3:0 | RO | Reserved |

1.10 OHCI HcBulkHeadED Register (UHO HcBulkHeadED)

Address: 0x9C1020A8

Reset: 0x00000000

Field Name | Bit | Access | Description |

BHED | 31:4 | RW | BulkHeadED |

Reserved | 3:0 | RO | Reserved |

1.11 OHCI HcBulkCurrentED Register (UHO HcBulkCurrentED)

Address: 0x9C1020AC

Reset: 0x00000000

Field Name | Bit | Access | Description |

BCED | 31:4 | RW | BulkCurrentED |

Reserved | 3:0 | RO | Reserved |

1.12 OHCI HcDoneHead Register (UHO HcDoneHead)

Address: 0x9C1020B0

Reset: 0x00000000

Field Name | Bit | Access | Description |

DH | 31:4 | RO | DoneHead |

Reserved | 3:0 | RO | Reserved |

1.13 OHCI HcFmInterval Register (UHO HcFmInterval)

Address: 0x9C1020B4

Reset: 0x27782EDF

| Field Name | Bit | Access | Description |

| FIT | 31 | RW | FrameIntervalToggle HCD toggles this bit whenever it loads a new value to FrameInterval. |

| FSMPS | 30:16 | RW | FSLargestDataPacket Default value is (FI-210)*6/7 |

| Reserved | 15:14 | RO | Reserved |

| FI | 13:0 | RW | Frame Interval Specify the interval between two consecutive SOFs in 12MHz. The nominal value is set to be 11,999. |

1.14 OHCI HcFmRemaining Register (UHO HcFmRemaining)

Address: 0x9C1020B8

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| FRT | 31 | RO | Frame Remaining Toggle This bit is loaded from the FrameIntervalToggle field of HcFmInterval whenever FrameRemaining reaches 0. |

| Reserved | 30:15 | RO | Reserved |

| FR | 14:0 | RO | Frame Remaining When it reaches zero, it is reset by loading the FrameInterval value specified in HcFmInterval at the next bit time boundary. |

1.15 OHCI HcFmNumber Register (UHO HcFmNumber)

Address: 0x9C1020BC

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| Reserved | 31:16 | RO | Reserved |

| FN | 15:0 | RO | FrameNumber |

1.16 OHCI HcPeriodicStart Register (UHO HcPeriodicStart)

Address: 0x9C1020C0

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| Reserved | 31:15 | RO | Reserved |

| PS | 14:0 | RW | PeriodicStart When HcFmRemaining reaches the value specified,processing of the periodic lists will have priority over Control/Bulk pro- cessing. |

1.17 OHCI HcLSThreshold Register (UHO HcLSThreshold)

Address: 0x9C1020C4

Reset: 0x00000628

Field Name | Bit | Access | Description |

Reserved | 31:8 | RO | Reserved |

LST | 7:0 | RW | LSThreshold |

1.18 OHCI HcRhDescriptorA Register (UHO HcRhDescriptorA)

Address: 0x9C1020C8

Reset: 0x01000101

| Field Name | Bit | Access | Description |

| POTPGT | 31:24 | RO | PowerOnToPowerGoodTime Not support |

| Reserved | 23:13 | RO | Reserved |

| NOCP | 12 | RO | NoOverCurrentProtection Read as '1', Not overcurrent protection support |

| OCPM | 11 | RO | OverCurrentProtectionMode Read as '0', Not support |

| DT | 10 | RO | DeviceType Read as '0', specified that the Root Hub is not a compound device. |

| NPS | 9 | RO | NoPowerSwitching Read as '1', ports are always powered on |

| PSM | 8 | RO | PowerSwitchingMode Read as '0', all ports are powered at the same time |

| NDP | 7:0 | RO | NumberDownstreamPorts The number of downstream ports supported by the Root Hub is 8'b1 |

1.19 OHCI HcRhDescriptorB Register (UHO HcRhDescriptorB)

Address: 0x9C1020CC

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| PPCM | 31:16 | RO | PortPowerControlMask Not support, read as 0x00 |

| DR | 15:0 | RW | DeviceRemovable Not support, read as 0x00 |

1.20 OHCI HcRhStatus Register (UHO HcRhStatus)

Address: 0x9C1020D0

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| CRWE | 31 | Other | (write) ClearRemoteWakeupEnable Writing a '1' clears DeviceRemoveWakeupEnable. Writing a '0' has no effect. |

| Reserved | 30:18 | RO | Reserved |

| CCIC | 17 | RO | OverCurrentIndicatorChange Not support |

| LPSC | 16 | RO | (read) LocalPowerStatusChange Read as '0', the Root Hub does not support the local power status feature (write) SetGlobalPower Not support. |

| DRWE | 15 | RW | (read) DeviceRemoteWakeupEnable This bit enables a ConnectStatusChange bit as a resume event, causing a USBSUSPEND to USBRESUME state tran- sition and setting the ResumeDetected interrupt. 0 = ConnectStatusChange is not a remote wakeup event. (default) 1 = ConnectStatusChange is a remote wakeup event. (write) SetRemoteWakeupEnable Writing a '1' sets De- viceRemoveWakeupEnable. Writing a '0' has no effect. |

| Reserved | 14:2 | RO | Reserved |

| OCI | 1 | RO | OverCurrentIndicator Read as '0', Not support |

| LPS | 0 | RO | (read) LocalPowerStatus Read as '0', the Root Hub does not support the local power status feature (write) ClearGlobalPower Not support |

1.21 OHCI HcRhPortStatus Register (UHO HcRhPortStatus)

Address: 0x9C1020D4

Reset: 0x00000100

| Field Name | Bit | Access | Description |

| Reserved | 31:21 | RO | Reserved |

| PRSC | 20 | W1C | PortResetStatusChange 0 = port reset is not complete 1 = port reset is complete |

| OCIC | 19 | RO | PortOverCurrentIndicatorChange Read as '0', no change in PortOverCurrentIndicator |

| PSSC | 18 | W1C | PortSuspendStatusChange 0 = resume is not completed 1 = resume completed |

| PESC | 17 | W1C | PortEnableStatusChange 0 = no change in PortEnableStatus 1 = change in PortEnableStatus |

| CSC | 16 | W1C | ConnectStatusChange 0 = no change in CurrentConnectStatus 1 = change in CurrentConnectStatus |

| Reserved | 15:10 | RO | Reserved |

| LSDA | 9 | Other | (read) LowSpeedDeviceAttached Indicates the speed of the device attached to this port. This field is valid only when the CurrentConnectStatus is set. 0 = full speed device attached 1 = low speed device attached (write) ClearPortPower HCD clears the PortPowerStatus bit by writing a '1' to this bit.Writing a '0' has no effect. |

| PPS | 8 | RO | (read) PortPowerStatus Read as '1', port power is on. (write) SetPortPower HCD writes a '1' to set the PortPowerStatus bit. Writing a '0' has no effect. |

| Reserved | 7:5 | RO | Reserved |

| PRS | 4 | Other | (read) PortResetStatus 0 = port reset signal is not active 1 = port reset signal is active (write) SetPortReset HCD sets the port reset signaling by writing a '1' to this bit.Writing a '0' has no effect. |

| POCI | 3 | Other | (read) PortOverCurrentIndicator Read as '0', no overcurrent condition (write) ClearSuspendStatus HCD writes a '1' to initiate a resume. Writing a '0' has no effect. A resume is initiated only if PortSuspendStatus is set. |

| PSS | 2 | Other | (read) PortSuspendStatus Indicate the port is suspended or in the resume sequence. 0 = port is not suspended 1 = port is suspended (write) SetPortSuspend The HCD sets the PortSuspendSta- tus bit by writing a '1' to this bit. Writing a '0' has no effect. |

| PES | 1 | Other | (read) PortEnableStatus Indicate whether the port is enabled or disabled. HCD sets this bit by writing SetPortEnable and clears it by writing ClearPortEnable. 0 = port is disabled 1 = port is enabled (write) SetPortEnable The HCD sets PortEnableStatus by writing a '1'.Writing a '0' has no effect. |

| CCS | 0 | Other | (read) CurrentConnectStatus 0 = no device connected 1 = device connected (write) ClearPortEnable 0 = Ignore 1 = clear the PortEnableStatus bit Note: This bit is always read '1b' when the attached device is nonremovable (DeviceRemoveable[NDP]). |

1.25 HcRhPortStatus Additional Register (UH PortStatusA)

Address: 0x9C1020E4

Reset: 0x00180B40

| Field Name | Bit | Access | Description |

| reserved | 31:23 | RO | RESERVED |

| CLK DIV2 5 | 22:16 | RW | Clock Divider for 2.5us from Slow Clock These bits are used to divide the slow clock to 2.5us pulse for remote wakeup use. default '24' for 10MHz clock |

| reserved | 15:12 | RO | RESERVED |

SAMPLE EN | 11 | RW | UTMI RX Negedge Sample Enable |

RXERR BLOCK EN | 10 | RW | PHY RXERR Signal Block Enable |

OUT TRIG | 9:8 | RW | OUT Transfer Trigger Level |

PHY SIM MODE | 7 | RW | PHY Simulation Mode |

LS TO CTRL | 6:4 | RW | Low Speed Timeout Control |

PORT PAR EN | 3 | RW | PHYCLK is able to stop in SUSPEND State |

reserved | 2:1 | RO | Reserved |

SUSPEND HCFS | 0 | RW | Suspend when HC in suspend state |

Group 2 USB Host EHCI Controller

2.0 EHCI Interface Version Number (UHE HCIVERSION)

Address: 0x9C102100

Reset: 0x01100020

| Field Name | Bit | Access | Description |

| HCIVERSION | 31:16 | RO | Interface Version Number The most significant byte of this register represents a major revision and the least significant byte is the minor revision. Read as '0110' |

| Reserved | 15:8 | RO | Reserved |

| CAPLENGTH | 7:0 | RO | Capability Register Length offset to add to register base to find the beginning of the Operational Register Space. Read as '20' |

2.1 EHCI Structural Parameters (UHE HCSPARAMS)

Address: 0x9C102104

Reset: 0x00001101

| Field Name | Bit | Access | Description |

| Reserved | 31:24 | RO | Reserved |

| DPN | 23:20 | RO | Debug Port Number |

| Reserved | 19:17 | RO | Reserved |

| P INDICATOR | 16 | RO | Port Indicators Not support, read as '0' |

| N CC | 15:12 | RO | Number of Companion Controller Read as '1', indicates the number of companion controllers associated with this USB 2.0 host controller. |

| N PCC | 11:8 | RO | Number of Ports per Companion Controller Read as '1', indicates the number of ports supported per companion host controller. |

PRR | 7 | RO | Port Routing Rules the next N PCC port are routed to the next lowest function com- panion controller, and so on. |

Reserved | 6:5 | RO | Reserved |

PPC | 4 | RO | Port Power Control |

N PORTS | 3:0 | RO | Number of PORTS |

2.2 EHCI Capability Parameters (UHE HCCPARAMS)

Address: 0x9C102108

Reset: 0x000A0006

| Field Name | Bit | Access | Description |

| Reserved | 31:20 | RO | Reserved |

| 32FPLC | 19 | RO | 32-Frame Periodic List Capability Read as '1', indicates 32-Frame Periodic List Capability is supported |

| PPCEC | 18 | RO | Per-Port Change Event Capability Read as '0', indicates per-port change event is not sup- ported |

| LPMC | 17 | RO | Link Power Management Capability Read as '1', indicates LPM is supported |

| HCP | 16 | RO | Hardware Prefetch Capability Read as '0', indicates no pre-fetch capability |

| EECP | 15:8 | RO | EHCI Extended Capabilities Pointer Read as '0', indicates no extended capabilities are imple- mented. |

| IST | 7:4 | RO | Isochronous Scheduling Threshold Read as '0', indicated no caching data structure during pe- riodic schedule traversal per micro-frame |

| Reserved | 3 | RO | Reserved |

ASPC | 2 | RO | Asynchronous Schedule Park Capability |

PFLF | 1 | RO | Programmable Frame List Flag |

AC | 0 | RO | 64-bit Addressing Capability |

2.3 EHCI Companion Port Route (UHE HCSP PORTROUTE)

Address: 0x9C10210C

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| HCSP PORTROUTE | 31:0 | RO | Companion Port Route Description Read as '0', not support |

2.8 EHCI USB Command (UHE USBCMD)

Address: 0x9C102120

Reset: 0x00080B00

| Field Name | Bit | Access | Description |

| Reserved | 31:28 | RO | Reserved |

| HIRD | 27:24 | RW | Host-Initiated Resume Duration in LPM ResumeK Length = 50us+75us*HIRD |

ITC | 23:16 | RW | Interrupt Threshold Control 0x00 Reserved |

PPCEE | 15 | RO | Per-Port Change Events Enable |

FSP | 14 | RO | Fully Synchronized Prefetch |

ASPE | 13 | RO | Asynchronous Schedule Prefetch Enable |

PSPE | 12 | RO | Periodic Schedule Prefetch Enable |

ASPME | 11 | RW | Asynchronous Schedule Park Mode Enable |

Reserved | 10 | RO | Reserved |

ASPMC | 9:8 | RW | Asynchronous Schedule Park Mode Count |

LHCR | 7 | RO | Light Host Controller Reset |

IAAD | 6 | Other | Interrupt on Async Advance Doorbell |

ASE | 5 | RW | Asynchronous Schedule Enable |

PSE | 4 | RW | Periodic Schedule Enable |

FLS | 3:2 | RW | Frame List Size |

HCRESET | 1 | Other | Host Controller Reset |

RS | 0 | RW | Run/Stop |

2.9 EHCI USB Status (UHE USBSTS)

Address: 0x9C102124

Reset: 0x00001000

| Field Name | Bit | Access | Description |

| PCD | 31:16 | RO | Port-n Change Detect Not supported, Read as 0x0000 |

ASS | 15 | RU | Asynchronous Schedule Status |

PSS | 14 | RU | Periodic Schedule Status |

Reclamation | 13 | RU | Reclamation |

HCH | 12 | RO | HCHalted |

Reserved | 11:6 | RO | Reserved |

IAA | 5 | W1C | Interrupt on Async Advance |

HSE | 4 | RO | Host System Error |

FLR | 3 | W1C | Frame List Rollover |

PCD | 2 | W1C | Port Change Detect |

USBERRINT | 1 | W1C | USB Error Interrupt |

USBINT | 0 | W1C | USB Interrupt |

2.10 EHCI USB Interrupt Enable (UHE USBINTR)

Address: 0x9C102128

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| PCEE | 31:16 | RO | Port-n Change Event Enable Not supported, read as 0x0000 |

| Reserved | 15:6 | RO | Reserved |

| IAAE | 5 | RW | Interrupt on Async Advance Enable Enable or disable Interrupt on Async Advance interrupt source in the USBSTS register. |

| HSEE | 4 | RW | Host System Error Enable Enable Host interrupt. |

| FLRE | 3 | RW | Frame List Rollover Enable Enable or disable Frame List Rollover interrupt source in the USBSTS register. |

| PCIE | 2 | RW | Port Change Interrupt Enable Enable or disable Port Change Detect interrupt source in the USBSTS register. |

| UEIE | 1 | RW | USB Error Interrupt Enable Enable or disable USBERRINT interrupt source in the US- BSTS register. |

| UIE | 0 | RW | USB Interrupt Enable Enable or disable USBINT interrupt source in the USBSTS register. |

2.11 EHCI USB Frame Index (UHE FRINDEX)

Address: 0x9C10212C

Reset: 0x00000000

Field Name | Bit | Access | Description |

Reserved | 31:14 | RO | Reserved |

FI | 13:0 | Other | Frame Index |

2.12 EHCI 4G Segment Selector (UHE CTRLDESSEGMENT)

Address: 0x9C102130

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| CTRLDSSEGMENT | 31:0 | RO | Control Data Structure Segment Not support, read as '0' |

2.13 EHCI Frame List Base Address (UHE PERIODICLISTBASE)

Address: 0x9C102134

Reset: 0x00000000

| Field Name | Bit | Access | Description |

| BA | 31:12 | RW | Base Address The beginning address of the periodic frame list in the sys- tem memory. |

| Reserved | 11:0 | RO | Reserved |

2.14 EHCI Next Asynchronous List Address (UHE ASYNCLISTADDR)

Address: 0x9C102138

Reset: 0x00000000

Field Name | Bit | Access | Description |

LPL | 31:5 | RW | Link Pointer Low |

Reserved | 4:0 | RO | Reserved |

2.24 EHCI Configured Flag Register (UHE CONFIGFLAG)

Address: 0x9C102160

Reset: 0x00000000

Field Name | Bit | Access | Description |

Reserved | 31:1 | RO | Reserved |

CF | 0 | RW | Configure Flag |

2.25 EHCI Port Status and Control (UHE PORTSC)

Address: 0x9C102164

Reset: 0x00003000

| Field Name | Bit | Access | Description |

| DEV Addr | 31:25 | RW | Address of Device which attached to this port Used for LPM function only. A value of 0 indicates no de- vice is present |

| Suspend ST | 24:23 | RO | Suspend Status(LPM) These two bits are used by software to determine whether the most recent L1 request was successfull, specifically: Value Meaning 0x0 Success: State transition was successfull(ACK) 0x1 Not Yet: Device was unable to enter the L1 state at this time (NYET) 0x2 Not Supported: Device does not support the L1 state (STALL) 0x3 Timeout/Error: Device failed to respond or an error occurred |

| WKOC E | 22 | RO | Wake on Over-current Enable Read as '0', not support. |

| WKDSCNNT E | 21 | RO | Wake on Disconnect Enable Default = 0b. Writing this bit to a one enables the port to be sensitive to device disconnects as wake-up events. |

| WKCNNT E | 20 | RO | Wake on Connect Enable Default = 0b. Writing this bit to a one enables the port to be sensitive to device connects as wake-up events. |

| PTC | 19:16 | RW | Port Test Control Default = 0000b. When this field is zero, the port is NOT operating in a test mode. A non-zero value indicates that it is operating in test mode and the specific test mode is indicated by the specific value. The encoding of the test mode bits are (0110b - 1111b are reserved) Bits Test Mode 0x0 Test mode not enabled 0x1 Test J STATE 0x2 Test K STATE 0x3 Test SE0 NAK 0x4 Test Packet 0x5 Test FORCE ENABLE |

PI | 15:14 | RO | Port Indicator |

PO | 13 | RW | Port Owner |

PP | 12 | RO | Port Power |

LS | 11:10 | RU | Line Status |

Suspend L1 | 9 | RW | Suspend using LPM L1 |

PR | 8 | Other | Port Reset |

Suspend | 7 | Other | Suspend |

FPR | 6 | RW | Force Port Resume |

OCC | 5 | RO | Over-current Change |

OCA | 4 | RO | Over-current Active |

PEC | 3 | W1C | Port Enable/Disable Change |

PE | 2 | Other | Port Enabled/Disabled |

CSC | 1 | W1C | Connect Status Change |

CCS | 0 | RO | Current Connect Status |

Group 8 USB OTG Controller

8.0 OTG transceiver work mode select (MODE SELECT)

Address: 0x9C102400

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:5 | RO | Reserved |

|

|

|

|

ADP SUPPORT | 3 | RW | support or not |

SRP SUPPORT | 2 | RW | support or not |

WORK MODE | 1:0 | RW | work mode select |

8.1 A/B-device control reg (OTG DEVICE CTRL)

Address: 0x9C102404

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:6 | RO | Reserved |

B HNP EN | 5 | Other | B-device has successfully accepted A-device set ture(b hnp en) cmd |

B BUS REQ | 4 | RW | B-device wants to use the bus or not |

A CLR ERR | 3 | Other | to clear a vbus err due to an overcurrent condition and causes the A-device to transition to a wait vfall |

A SET B HNP EN | 2 | RW | A-device has successfully set the b hnp enable bit in the |

A BUS REQ | 1 | RW | A-device wants to use the bus |

A BUS DROP | 0 | Other | A-device wants to power down the bus |

8.2 OTG transceiver interrupt enable (OTG INT EN)

Address: 0x9C102408

Reset:0 x0

| Field Name | Bit | Access | Description |

| Reserved | 31:10 | RO | Reserved |

| ADP CHANGE EN | 9 | RW | adp change 0: Disable(default) 1: Enable |

| A SRP DET EN | 8 | RW | A-device has detected SRP 0: Disable(default) 1: Enable |

| B AIDL BDIS EN | 7 | RW | B-device disconnects to A-device to start HNP 0: Disable(default) 1: Enable |

| A BIDL ADIS EN | 6 | RW | A-device disconnects to B-device to end HNP 0: Disable(default) 1: Enable |

| A AIDL BDIS TMOUT EN | 5 | RW | waiting for a disconnect tmout when HNP 0: Disable(default) 1: Enable |

B SRP FAIL EN | 4 | RW | B-Device SRP fail |

BDEV CONNECT TMOUT EN | 3 | RW | A-Device waits B-Device Connect timeout |

VBUS RISE TMOUT EN | 2 | RW | A-Device waits vbus valid timeout |

ID CHANGE EN | 1 | RW | id pin has changed |

OVERCURRENT EN | 0 | RW | an attached B-device draws more current |

8.3 OTG transceiver status and interrupt flag (OTG ST)

Address: 0x9C10240C

Reset: 0x0001 0000

| Field Name | Bit | Access | Description |

| Reserved | 31:17 | RO | Reserved |

| ID | 16 | RO | the sampling value of the analog Id line used in OTG mode Default:1 |

| Reserved | 15:10 | RO | Reserved |

| ADP CHANGE IF | 9 | Other | adp change high active, write 1 to clear this flag |

| A SRP DET IF | 8 | Other | A-device has detected SRP high active, write 1 to clear this flag |

| B AIDL BDIS IF | 7 | Other | B-device disconnects to A-device to start HNP high active, write 1 to clear this flag |

| A BIDL ADIS IF | 6 | Other | A-device disconnects to B-device to end HNP high active, write 1 to clear this flag |

| A AIDL BDIS TMOUT IF | 5 | Other | waiting for a disconnect tmout when HNP high active, write 1 to clear this flag |

B SRP FAIL IF | 4 | Other | B-Device SRP fail |

BDEV CONNECT TMOUT IF | 3 | Other | A-Device waits B-Device Connect timeout |

VBUS RISE TMOUT IF | 2 | Other | A-Device waits vbus valid timeout |

ID CHANGE IF | 1 | Other | id pin has changed |

OVERCURRENT IF | 0 | Other | an attached B-device draws more current |

8.4 Wait voltage on Vbus to go into regulation (A WAIT VRISE TMR)

Address: 0x9C102410

Reset: 0x0001 86A0

| Field Name | Bit | Access | Description |

| Reserved | 31:17 | RO | Reserved |

| A WAIT VRISE TMR | 16:0 | RW | used by A-device to wait for the voltage on Vbus to go into regulation Default:0x186a0(100ms, spec max) |

8.5 Session end to SRP init (B SSEND SRP TMR)

Address: 0x9C102414

Reset: 0x0016 E360

| Field Name | Bit | Access | Description |

| Reserved | 31:21 | RO | Reserved |

| B SSEND SRP TMR | 20:0 | RW | session end to SRP init Default:0x16E360(1.5s ,spec min) |

8.6 SE0 time before SRP (B SE0 SRP TMR)

Address: 0x9C102418

Reset: 0x000F 4240

| Field Name | Bit | Access | Description |

| Reserved | 31:20 | RO | Reserved |

| B SE0 SRP TMR | 19:0 | RW | SE0 time before SRP Default:0xF4240(1s ,spec min) |

8.7 Data-line pulse time (B DATA PLS TMR)

Address: 0x9C10241C

Reset: 0x0000 1B58

| Field Name | Bit | Access | Description |

| Reserved | 31:14 | RO | Reserved |

| B DATA PLS TMR | 13:0 | RW | Data-line pulse time Default:0x1B58(7ms ,spec: 5ms-10ms) |

8.8 SRP fail time (B SRP FAIL TMR)

Address: 0x9C102420

Reset: 0x005B 8D80

| Field Name | Bit | Access | Description |

| Reserved | 31:23 | RO | Reserved |

| B SRP FAIL TMR | 22:0 | RW | SRP fail time Default:0x5B8D80(6s ,spec max) |

8.9 Session valid to B-connect (B SVLD BCON TMR)

Address: 0x9C102424

Reset: 0x0001 86A0

| Field Name | Bit | Access | Description |

| Reserved | 31:20 | RO | Reserved |

| B SVLD BCON TMR | 19:0 | RW | Session valid to B-connect Default:0x186A0(100ms ,spec: 1s max) |

8.10 A-idle to B-disconnect time (B AIDL BDIS TMR)

Address: 0x9C102428

Reset: 0x0000 1388

| Field Name | Bit | Access | Description |

| Reserved | 31:18 | RO | Reserved |

| B AIDL BDIS TMR | 17:0 | RW | A-idle to B-disconnect time Default:0x1388(5ms) |

8.11 B-disconnect to A-connect time (A BDIS ACON TMR)

Address: 0x9C10242C

Reset: 0x0000 2710

| Field Name | Bit | Access | Description |

| Reserved | 31:18 | RO | Reserved |

| A BDIS ACON TMR | 17:0 | RW | B-disconnect to A-connect time Default:0x2710(10ms) |

8.12 Local disconnect to data line discharge time (LDIS DSCHG TMR)

Address: 0x9C102430

Reset: 0x0000 0015

Field Name | Bit | Access | Description |

Reserved | 31:5 | RO | Reserved |

LDIS DSCHG TMR | 4:0 | RW | Local disconnect to data line discharge time |

8.13 B-connect short debounce (A BCON SDB TMR)

Address: 0x9C102434

Reset: 0x0000 0003

| Field Name | Bit | Access | Description |

| Reserved | 31:17 | RO | Reserved |

| A BCON SDB TMR | 16:0 | RW | B-Connect short de-bounce Default:0x00003(3us) |

8.14 B-connect long debounce (A BCON LDB TMR)

Address: 0x9C102438

Reset: 0x0001 86A0

| Field Name | Bit | Access | Description |

| Reserved | 31:17 | RO | Reserved |

| A BCON LDB TMR | 16:0 | RW | B-connect long de-bounce Default:0x186A0(100ms) |

8.15 A-device ADP probing period (A ADP PRB TMR)

Address: 0x9C10243C

Reset:0x001A B3F0

| Field Name | Bit | Access | Description |

| Reserved | 31:22 | RO | Reserved |

| A ADP PRB TMR | 21:0 | RW | A-device ADP probing period Default:0x1AB3F0(1.75s) |

8.16 B-device ADP probing period (B ADP PRB TMR)

Address: 0x9C102440

Reset: 0x001E 8480

| Field Name | Bit | Access | Description |

| Reserved | 31:22 | RO | Reserved |

| B ADP PRB TMR | 21:0 | RW | B-device ADP probing period Default:0x1E8480(2s) |

8.17 B-device ADP detach time (B ADP DETACH TMR)

Address: 0x9C102444

Reset: 0x0030 D400

| Field Name | Bit | Access | Description |

| Reserved | 31:22 | RO | Reserved |

| B ADP DETACH TMR | 21:0 | RW | B-device ADP detach time Default:0x30D400(3.2s ,spec: 3s-3.4s) |

8.18 ADP change precision (ADP CHNG PRECISION)

Address: 0x9C102448

Reset: 0x0000 01FF

| Field Name | Bit | Access | Description |

| Reserved | 31:12 | RO | Reserved |

| ADP CHNG PRECISION | 11:0 | RW | ADP change precision Default:0x1FF(512us) |

8.19 Seesion end to Votg vbus lkg (A WAIT VFALL TMR)

Address: 0x9C10244C

Reset: 0x000F 4240

| Field Name | Bit | Access | Description |

| Reserved | 31:20 | RO | Reserved |

| A WAIT VFALL TMR | 19:0 | RW | Seesion end to Votg vbus lkg Default:0xF4240(1s) |

8.20 Wait for B-connect time (A WAIT BCON TMR)

Address: 0x9C102450

Reset: 0x0010 C8E0

| Field Name | Bit | Access | Description |

| Reserved | 31:25 | RO | Reserved |

| A WAIT BCON TMR | 24:0 | RW | Wait for B-connect time Default:0x10C8E0(1.1s) |

8.21 A-idle to B-disconnect time (A AIDL BDIS TMR)

Address: 0x9C102454

Reset: 0x0003 0D40

| Field Name | Bit | Access | Description |

| Reserved | 31:18 | RO | Reserved |

| A AIDL BDIS TMR | 17:0 | RW | A-idle to B-disconnect time Default:0x30D40(200ms) |

8.22 A-SE0 to B-reset time (B ASE0 BRST TMR)

Address: 0x9C102458

Reset: 0x0002 5D78

| Field Name | Bit | Access | Description |

| Reserved | 31:18 | Reserved | |

| B ASE0 BRST TMR | 17:0 | A-SE0 to B-reset time Default:0x25D78(155ms) |

8.23 B-idle to A-disconnect time (A BIDL ADIS TMR)

Address: 0x9C10245C

Reset: 0x0002 5D78

| Field Name | Bit | Access | Description |

| Reserved | 31:18 | RO | Reserved |

| A BIDL ADIS TMR | 17:0 | RW | B-idle to A-disconnect time Default:0x25D78(155ms) |

8.24 ADP Dis-Charge VBus time (ADP CHRG TIME)

Address: 0x9C102460

Reset: 0x0000 0898

| Field Name | Bit | Access | Description |

| Reserved | 31:13 | RO | Reserved |

| ADP CHRG TIME | 12:0 | RW | ADP Dis-Charge VBUS time Default:0x0898(2.2ms, This is also used as the maximum time for charge VBUS) |

8.25VBUS Pulse time (VBUS PULSE TIME)

Address: 0x9C102464

Reset: 0x0000 7530

| Field Name | Bit | Access | Description |

| Reserved | 31:15 | RO | Reserved |

| VBUS PULSE TIME | 14:0 | RW | VBus pulse time Default:0x7530(30ms) |

8.26 A B-con SDB window time (A BCON SDB WIN)

Address: 0x9C102468

Reset: 0x0001 86A0

| Field Name | Bit | Access | Description |

| Reserved | 31:17 | RO | Reserved |

| A BCON SDB WIN | 16:0 | RW | A B-Con SDB window time Default:0x186A0(100ms) |

8.27 OTG Transceiver debug registers (OTG DEBUG REG)

Address: 0x9C10246C

Reset: 0x0000 0088

Field Name | Bit | Access | Description |

Reserved | 31:30 | RO | Reserved |

ADPC1 | 29:16 | RO | A rising couner1 for debug |

SEND | 15:14 | RO | Sessend from PHY |

VVLD | 13:12 | RO | VBUS Valid from PHY |

BVLD | 11:10 | RO | B VBUS vallid from PHY |

AVLD | 9:8 | RO | A VBUS valid from PHY |

FSM PS | 7:4 | RO | OTG FSM previous state when enter vbus error |

FSM CS | 3:0 | RO | OTG FSM current state |

8.28 OTG ADP rising Couner for debug (OTG ADPCNT REG)

Address: 0x9C102470

Reset: 0x0

| Field Name | Bit | Access | Description |

| Reserved | 31:30 | RO | Reserved |

ADPC0 | 29:16 | RO | A rising couner0 for debug |

Reserved | 15:14 | RO | Reserved |

ADPC2 | 13:0 | RO | A rising couner2 for debug |

8.29 A-device ADP drive Vbus time when detect change (A ADP VBUS)

Address: 0x9C102474

Reset: 0x1A B3F0

| Field Name | Bit | Access | Description |

| Reserved | 31:22 | RO | Reserved |

| ADP VBUS TIM | 21:0 | RW | A-device ADP drive vubs time This timer is started at the beginning of dis-charge vbus |

Group 16 USB Device: DMA Control

16.0 EP12 DMA Control Status (UEP12DMACS)

Address: 0x9C102800

Reset: 0x0800 0000

| Field Name | Bit | Access | Description |

| DMA EN | 31 | Other | DMA enable, it will be auto-clear to 0 when DMA fin- ishes |