12. Pulse Width Modulation (PWM)

12.1 Introduction

The SP7021 support 8 sets PWM module output. The PWM module can base on system clock to produce PWM signals. The PWM frequency and duty can be set by registers. The PWM control registers locate in RGST Table Group 244 which memory map to address 0x9C007A00~0x9C007A7F.

12.2 Function Diagram

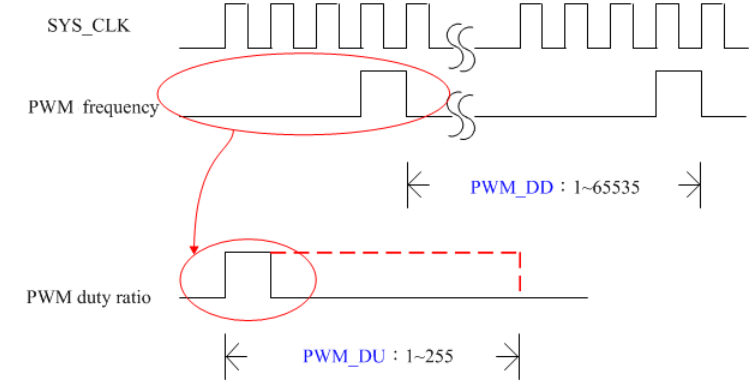

A generalized function diagram of PWM is shown in Figure 12-1.

Figure 12-1 PWM Function Diagram

12.2.1 PWM Frequency

There are 4 PWM duty divisor can be selected as PWM frequency source. Each PWM module should choose one PWM duty divisor to decide its output frequency. The PWM duty divisor control registers are Group 244.2~5. The PWM duty divisor source select registers are Group 244.6~13. For example, set PWM duty divisor value in PWM_DD0, than the PWM frequency = 1/((1/sysclk)*PWM_DD0*256). For example, PWM sysclk is 202.5MHz, PWM_DD0 set as 0x1EE6(=7910), then PWM period will be 0.01s, PWM frequency will be 100Hz.

12.2.2 PWM Duty

PWM duty can be changed by set PWM duty ratio which in Group 244.6~13 bit[7:0]. The PWM duty ratio can set value to 1~255.

12.3 Registers Map

12.3.1 Registers Memory Map

Address | Group No. | Register Name | Description |

|---|---|---|---|

0x9C007A00 | G244.0 | PWM MODE0 | PWM mode control |

0x9C007A04 | G244.1 | PWM MODE1 | PWM DD count enable |

0x9C007A08 | G244.2 | PWM DD0 | PWM duty divisor |

0x9C007A0C | G244.3 | PWM DD1 | PWM duty divisor |

0x9C007A10 | G244.4 | PWM DD2 | PWM duty divisor |

0x9C007A14 | G244.5 | PWM DD3 | PWM duty divisor |

0x9C007A18 | G244.6 | PWM0 CFG | PWM config |

0x9C007A1C | G244.7 | PWM1 CFG | PWM config |

0x9C007A20 | G244.8 | PWM2 CFG | PWM config |

0x9C007A24 | G244.9 | PWM3 CFG | PWM config |

0x9C007A28 | G244.10 | PWM4 CFG | PWM config |

0x9C007A2C | G244.11 | PWM5 CFG | PWM config |

0x9C007A30 | G244.12 | PWM6 CFG | PWM config |

0x9C007A34 | G244.13 | PWM7 CFG | PWM config |

12.3.2 Registers Description

RGST Table Group 244 DISP PWM

244.0 PWM mode control (PWM MODE0)

Address: 0x9C007A00

Reset: 0x0000

Field Name | Bit | Access | Description |

PWM BYPASS | 15:8 | RW | PWM bypass control enable |

| PWM EN | 7:0 | RW | PWM enable |

244.1 PWM DD count enable (PWM MODE1)

Address: 0x9C007A04

Reset: 0x0F00

| Field Name | Bit | Access | Description |

| reserved0 | 15:12 | RO | |

| PWM DD3 SYNC OFF | 11 | RW | PWM duty divisor count 3 sync off PWM phase do sync format timing 0: Turn ON 1: Turn OFF (default) |

| PWM DD2 SYNC OFF | 10 | RW | PWM duty divisor count 2 sync off PWM phase do sync format timing 0: Turn ON 1: Turn OFF (default) |

PWM DD1 SYNC OFF | 9 | RW | PWM duty divisor count 1 sync off |

PWM DD0 SYNC OFF | 8 | RW | PWM duty divisor count 0 sync off |

reserved1 | 7:5 | RO | |

reserved2 | 4 | RO | |

PWM CNT3 EN | 3 | RW | PWM DD3 count enable |

PWM CNT2 EN | 2 | RW | PWM DD2 count enable |

PWM CNT1 EN | 1 | RW | PWM DD1 count enable |

PWM CNT0 EN | 0 | RW | PWM DD0 count enable |

244.2 PWM duty divisor (PWM DD0)

Address: 0x9C007A08

Reset: 0x000A

| Field Name | Bit | Access | Description |

| PWM DD0 | 15:0 | RW | PWM duty divisor PWM period = (1 / sys clk * PWM DD0) * 256 |

244.3 PWM duty divisor (PWM DD1)

Address: 0x9C007A0C

Reset: 0x000A

| Field Name | Bit | Access | Description |

| PWM DD1 | 15:0 | RW | PWM duty divisor PWM period = (1 / sys clk * PWM DD1) * 256 |

244.4 PWM duty divisor (PWM DD2)

Address: 0x9C007A10

Reset: 0x000A

| Field Name | Bit | Access | Description |

| PWM DD2 | 15:0 | RW | PWM duty divisor PWM period = (1 / sys clk * PWM DD2) * 256 |

244.5 PWM duty divisor (PWM DD3)

Address: 0x9C007A14

Reset: 0x000A

Field Name | Bit | Access | Description |

PWM DD3 | 15:0 | RW | PWM duty divisor |

244.6 PWM0 config (PWM0 CFG)

Address: 0x9C007A18

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved2 | 15:1 | RO | |

| PWM DD0 SEL | 9:8 | RW | PWM duty divisor source select 0x0: PWM DD0 (default) 0x1: PWM DD1 0x2: PWM DD2 0x3: PWM DD3 |

| PWM DD0 | 7:0 | RW | PWM duty ratio |

244.7 PWM config (PWM1 CFG)

Address: 0x9C007A1C

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved3 | 15:10 | RO | |

| PWM DD1 SEL | 9:8 | RW | PWM duty divisor source select 0x0: PWM DD0 (default) 0x1: PWM DD1 0x2: PWM DD2 0x3: PWM DD3 |

| PWM DD1 | 7:0 | RW | PWM duty ratio region 1-255 |

244.8 PWM config (PWM2 CFG)

Address: 0x9C007A20

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved4 | 15:10 | RO | |

| PWM DD2 SEL | 9:8 | RW | PWM duty divisor source select 0x0 : PWM DD0 (default) 0x1 : PWM DD1 0x2 : PWM DD2 0x3 : PWM DD3 |

| PWM DD2 | 7:0 | RW | PWM duty ratio region 1-255 |

244.9 PWM config (PWM3 CFG)

Address: 0x9C007A24

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved5 | 15:10 | RO | |

| PWM DD3 SEL | 9:8 | RW | PWM duty divisor source select 0x0 : PWM DD0 (default) 0x1 : PWM DD1 0x2 : PWM DD2 0x3 : PWM DD3 |

| PWM DD3 | 7:0 | RW | PWM duty ratio region 1-255 |

244.10 PWM config (PWM4 CFG)

Address: 0x9C007A28

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved6 | 15:10 | RO | |

| PWM DD4 SEL | 9:8 | RW | PWM duty divisor source select 0x0 : PWM DD0 (default) 0x1 : PWM DD1 0x2 : PWM DD2 0x3 : PWM DD3 |

| PWM DD4 | 7:0 | RW | PWM duty ratio region 1-255 |

244.11PWM config (PWM5 CFG)

Address: 0x9C007A2C

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved7 | 15:10 | RO | |

| PWM DD5 SEL | 9:8 | RW | PWM duty divisor source select 0x0 : PWM DD0 (default) 0x1 : PWM DD1 0x2 : PWM DD2 0x3 : PWM DD3 |

| PWM DD5 | 7:0 | RW | PWM duty ratio region 1-255 |

244.12 PWM config (PWM6 CFG)

Address: 0x9C007A30

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved8 | 15:10 | RO | |

| PWM DD6 SEL | 9:8 | RW | PWM duty divisor source select 0x0 : PWM DD0 (default) 0x1 : PWM DD1 0x2 : PWM DD2 0x3 : PWM DD3 |

| PWM DD6 | 7:0 | RW | PWM duty ratio region 1-255 |

244.13 PWM config (PWM7 CFG)

Address: 0x9C007A34

Reset: 0x0001

Field Name | Bit | Access | Description |

| reserved9 | 15:10 | RO | |

| PWM DD7 SEL | 9:8 | RW | PWM duty divisor source select |

| PWM DD7 | 7:0 | RW | PWM duty ratio |