9. Interrupt Controller

9.1 Introduction

The SP7021 interrupt controller is a centralized resource for supporting and managing interrupts in a system. It provides low latency interrupt processing and efficient processing of arriving interrupts. Set registers for managing interrupt sources and interrupt behaviors. The interrupt mask, output FIQ/IRQ pins, trigger type and polarity all determined by register setting. The control registers locate at RGST Table Group15 and 21 which memory map are 0x9C000780~0x9C0007FF and 0x9C000A80~0x9C000AFF.

.

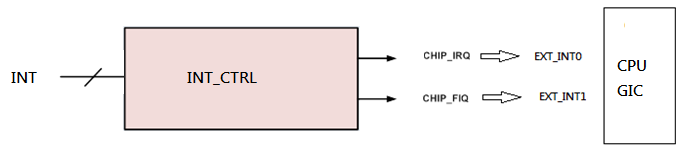

9.2 Function Diagram

A generalized function diagram of interrupt controller is shown in Figure 9-1.

Figure 9-1 Interrupt Controller Functional Blocks

- CPU GIC: ARM Cortex A7 generic interrupt controller.

- INT_CTRL: Device interrupt controller. The interrupt source can come from internal device or external pins.

9.3 Interrupt Source

There are totally 200 interrupt sources defined in SP7021. They are listed in Table 9-1. The table also shows the interrupt trigger type and clock source for each interrupt. The interrupt trigger type can be selected as edge or level trigger, the control registers define in Group15.0~6.

No | Description | Hardware Name | Level/Edge Trigger | Clock Source |

|---|---|---|---|---|

0 | TEGN | TGEN_INT_FIELD_START | Edge | SYSCLK |

1 | TGEN | TGEN_INT_FIELD_END | Edge | SYSCLK |

4 | TGEN | TGEN_INT1_USER | Edge | SYSCLK |

5 | TGEN | TGEN_INT2_USER | Edge | SYSCLK |

10 | USBC1 | USBC1_OTG_INT | level | SYSCLK |

11 | USBC0 | USBC0_OTG_INT | level | SYSCLK |

13 | USBC0 | USBC0_DEVICE_INT | Level | SYSCLK |

14 | USBC0 | USBC0_EHCI_INT | Level | SYSCLK |

15 | USBC0 | USBC0_OHCI_INT | Level | SYSCLK |

16 | USBC1 | USBC1_DEVICE_INT | Level | SYSCLK |

17 | USBC1 | USBC1_EHCI_INT | Level | SYSCLK |

18 | USBC1 | USBC1_OHCI_INT | Level | SYSCLK |

20 | CARD0(EMMC) | CARD_CTL0_INT | level | SYSCLK |

21 | CARD1(SD) | CARD_CTL1_INT | level | SYSCLK |

22 | CARD_CTL4(SDIO) | CARD_CTL4_INT | Level | SYSCLK |

25 | RBUS | RBUS_INTERRUPT | Level | 200MHz |

28 | SECURITY | SDPROT_INT | Level | SYSCLK |

29 | From FPGA | PI_EXT0_INT | Level | SYSCLK |

30 | From FPGA | PI_EXT1_INT | Level | SYSCLK |

36 | UPHY0 | UPHY0_INT | Level | SYSCLK |

37 | UPHY1 | UPHY1_INT | Level | SYSCLK |

41 | IOP | IOP_INT0 | Level | SYSCLK |

42 | IOP | IOP_INT1 | Level | SYSCLK |

49 | MIPI | CSI0_INT_FIELD_START | Edge | SYSCLK |

50 | MIPI | CSI0_INT_FIELD_END | Edge | SYSCLK |

51 | MIPI | CSI1_INT_FIELD_START | Edge | SYSCLK |

52 | MIPI | CSI1_INT_FIELD_END | Edge | SYSCLK |

53 | UART0 | UA0_INT | Level | 27MHz |

54 | UART1 | UA1_INT | Level | 27MHz |

55 | UART2 | UA2_INT | Level | 27MHz |

56 | UART3 | UA3_INT | Level | 27MHz |

58 | BCH | BCH_INT | Level | SYSCLK |

59 | AUD | LOSD_INT | edge | SYSCLK |

60 | AUD | AUD_FIFO_INT | level | SYSCLK |

66 | Ethernet Switch | L2SW_INT | Level | SYSCLK |

67 | SPI_COMBO | SPI_COMBO_1_DMA_W_INT | Level | SYSCLK |

68 | SPI_COMBO | SPI_SLAVE_1_RISC_INT | Level | SYSCLK |

69 | SPI_COMBO | SPI_MASTER_1_RISC_INT | Level | SYSCLK |

70 | SPI_COMBO | SPI_COMBO_2_DMA_W_INT | Level | SYSCLK |

71 | SPI_1OMBO | SPI_SLAVE_2_RISC_INT | Level | SYSCLK |

72 | SPI_COMBO | SPI_MASTER_2_RISC_INT | Level | SYSCLK |

73 | SPI_COMBO | SPI_COMBO_3_DMA_W_INT | Level | SYSCLK |

74 | SPI_COMBO | SPI_SLAVE_3_RISC_INT | Level | SYSCLK |

75 | SPI_COMBO | SPI_MASTER_3_RISC_INT | Level | SYSCLK |

92 | Input Capture | ICM_INT0 | Edge | SYSCLK |

93 | Input Capture | ICM_INT1 | Edge | SYSCLK |

94 | Input Capture | ICM_INT2 | Edge | SYSCLK |

95 | Input Capture | ICM_INT3 | Edge | SYSCLK |

103 | AXI Global Monitor interrupt | AXI_MON_INT | level | 200MHz |

105 | HDMI_TX | HDMI_TX_INT | level | SYSCLK |

120 | Interrupt from analog | PI_GPIO_INT0 | Programmable | 27MHz |

121 | Interrupt from analog | PI_GPIO_INT1 | Programmable | 27MHz |

122 | Interrupt from analog | PI_GPIO_INT2 | Programmable | 27MHz |

123 | Interrupt from analog | PI_GPIO_INT3 | Programmable | 27MHz |

124 | Interrupt from analog | PI_GPIO_INT4 | Programmable | 27MHz |

125 | Interrupt from analog | PI_GPIO_INT5 | Programmable | 27MHz |

126 | Interrupt from analog | PI_GPIO_INT6 | Programmable | 27MHz |

127 | Interrupt from analog | PI_GPIO_INT7 | Programmable | 27MHz |

128 | CBDMA for System | CBDMA0_INT | Level | 200MHz |

129 | CBDMA for System | CBDMA1_INT | Level | 200MHz |

134 | UART4 | UA4_INT | Level | 27MHz |

135 | UART5 | RESERVED | Level | 27MHz |

138 | UART DMA0 | UADMA0_INT | Level | SYSCLK |

139 | UART DMA1 | UADMA1_INT | Level | SYSCLK |

142 | UART2AXI | UADBG_INT | Level | SYSCLK |

143 | SPI_FLASH | SPI_INT | level | SYSCLK |

144 | SPI_COMBO | SPI_COMBO_0_DMA_W_INT | Level | SYSCLK |

145 | SPI_COMBO | SPI_SLAVE_0_RISC_INT | Level | SYSCLK |

146 | SPI_COMBO | SPI_MASTER_0_RISC_INT | Level | SYSCLK |

148 | SECURITY | sec_int | Level | SYSCLK |

149 | SPI_NAND | SPI_ND_INT | level | SYSCLK |

150 | STC | STC_INTERRUPT_TIMERW | Level | SYSCLK |

151 | STC | STC_INTERRUPT_TIMER0 | Edge | SYSCLK |

152 | STC | STC_INTERRUPT_TIMER1 | Edge | SYSCLK |

153 | STC | STC_INTERRUPT_TIMER2B | Edge | SYSCLK |

154 | STC | STC_INTERRUPT_TIMER3B | Edge | SYSCLK |

155 | STC_AV0 | STC_AV0_INTERRUPT_TIMER0 | Edge | SYSCLK |

156 | STC_AV0 | STC_AV0_INTERRUPT_TIMER1 | Edge | SYSCLK |

157 | STC_AV0 | STC_AV0_INTERRUPT_TIMER2B | Edge | SYSCLK |

158 | STC_AV0 | STC_AV0_INTERRUPT_TIMER3B | Edge | SYSCLK |

159 | STC_AV1 | STC_AV1_INTERRUPT_TIMER0 | Edge | SYSCLK |

160 | STC_AV1 | STC_AV1_INTERRUPT_TIMER1 | Edge | SYSCLK |

161 | STC_AV1 | STC_AV1_INTERRUPT_TIMER2B | Edge | SYSCLK |

162 | STC_AV1 | STC_AV1_INTERRUPT_TIMER3B | Edge | SYSCLK |

163 | RTC | SYS_RTC_INT | Edge | SYSCLK |

164 | STC_AV2 | STC_AV2_INTERRUPT_TIMER0 | Edge | SYSCLK |

165 | STC_AV2 | STC_AV2_INTERRUPT_TIMER1 | Edge | SYSCLK |

166 | STC_AV2 | STC_AV2_INTERRUPT_TIMER2B | Edge | SYSCLK |

167 | STC_AV2 | STC_AV2_INTERRUPT_TIMER3B | Edge | SYSCLK |

168 | STC_AV0 | STC_AV0_INTERRUPT_TIMERW | Level | SYSCLK |

174 | I2CMASTER0 | I2CM0_INT | Level | 27MHz |

175 | I2CMASTER1 | I2CM1_INT | Level | 27MHz |

176 | I2CMASTER2 | I2CM2_INT | Level | 27MHz |

177 | I2CMASTER3 | I2CM3_INT | Level | 27MHz |

178 | I2CDDC0 | DDC0_INT | Level | 27MHz |

182 | CHIPCPU0_DIRECT_INT0 | Edge | SYSCLK | |

183 | CHIPCPU0_DIRECT_INT1 | Edge | SYSCLK | |

184 | CHIPCPU0_DIRECT_INT2 | Edge | SYSCLK | |

185 | CHIPCPU0_DIRECT_INT3 | Edge | SYSCLK | |

186 | CHIPCPU0_DIRECT_INT4 | Edge | SYSCLK | |

187 | CHIPCPU0_DIRECT_INT5 | Edge | SYSCLK | |

188 | CHIPCPU0_DIRECT_INT6 | Edge | SYSCLK | |

189 | CHIPCPU0_DIRECT_INT7 | Edge | SYSCLK | |

198 | CHIPCPU0_INT | Edge | SYSCLK |

Table 9-1 Interrupt Source Table

9.4 Interrupt Polarity and Priority

The interrupt polarity can set as high active or low active by Group 15.7~13 registers. The interrupt priority can be set as FIQ or IRQ by Group 15.14~20 registers.

9.5 Interrupt Mask and Clear

The interrupt can be disable by set mask bit as 0. When set mask bit as 0, it means interrupt masked. The interrupt mask control registers locate at Group 15.21~27.

After interrupt event manage finished, the pending interrupt should be clear. The interrupt clear control registers locate at Group 21.0~6.

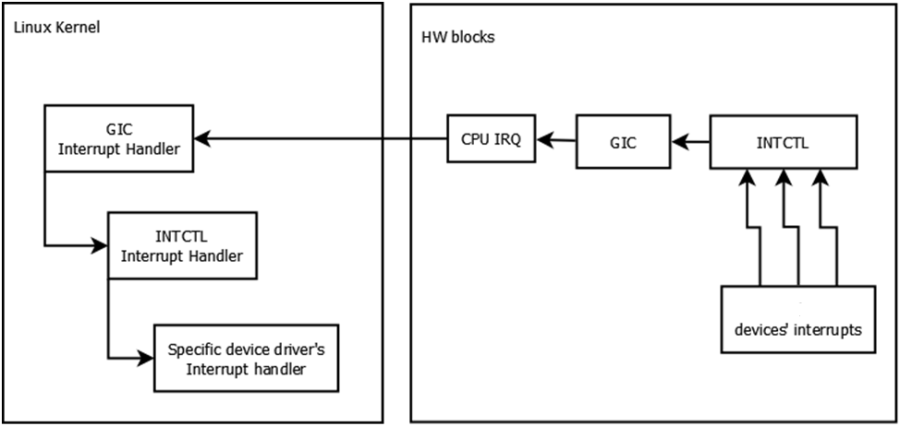

9.6 Interrupt Handler

Figure 9-2 shows the interrupt handler procedule.

Figure 9-2 Interrupt Handler

When CPU IRQ is raised, the operation flow should be as below procedure.

- GIC interrupt handler checks if it's INT_EXT0 or INT_EXT1. If so, call INTCTL handler to handle interrupts.

- INTCTL handler check G21.31 intr_group [14:0] to find out which pending register (G21.7~G21.20) has pending interrupt numbers.

- Read the pending register (G21.7~G21.20) to find out pending interrupt number.

- Mask the pending interrupt number by writing 0 to the corresponding bit in G15.21~G15.27

- Clear the pending interrupt number by writing 1 to the corresponding bit in G21.0~G21.6

- Call device-specific interrupt handler for this number

- Unmask the pending interrupt number by writing 1 to the corresponding bit in G15.21~G15.27

9.7 Registers Map

9.7.1 Registers Memory Map

Address | Group No. | Register Name | Description |

|---|---|---|---|

0x9C000780 | G15.0 | intr type[0] | Interrupt type register0 |

0x9C000784 | G15.1 | intr type[1] | Interrupt type register1 |

0x9C000788 | G15.2 | intr type[2] | Interrupt type register2 |

0x9C00078C | G15.3 | intr type[3] | Interrupt type register3 |

0x9C000790 | G15.4 | intr type[4] | Interrupt type register4 |

0x9C000794 | G15.5 | intr type[5] | Interrupt type register5 |

0x9C000798 | G15.6 | intr type[6] | Interrupt type register6 |

0x9C00079C | G15.7 | intr polarity[0] | Interrupt polarity register0 |

0x9C0007A0 | G15.8 | intr polarity[1] | Interrupt polarity register1 |

0x9C0007A4 | G15.9 | intr polarity[2] | Interrupt polarity register2 |

0x9C0007A8 | G15.10 | intr polarity[3] | Interrupt polarity register3 |

0x9C0007AC | G15.11 | intr polarity[4] | Interrupt polarity register4 |

0x9C0007B0 | G15.12 | intr polarity[5] | Interrupt polarity register5 |

0x9C0007B4 | G15.13 | intr polarity[6] | Interrupt polarity register6 |

0x9C0007B8 | G15.14 | CA7 priority[0] | CA7 priority register0 |

0x9C0007BC | G15.15 | CA7 priority[1] | CA7 priority register1 |

0x9C0007C0 | G15.16 | CA7 priority[2] | CA7 priority register2 |

0x9C0007C4 | G15.17 | CA7 priority[3] | CA7 priority register3 |

0x9C0007C8 | G15.18 | CA7 priority[4] | CA7 priority register4 |

0x9C0007CC | G15.19 | CA7 priority[5] | CA7 priority register5 |

0x9C0007D0 | G15.20 | CA7 priority[6] | CA7 priority register6 |

0x9C0007D4 | G15.21 | CA7 intr mask[0] | CA7 interrupt mask register0 |

0x9C0007D8 | G15.22 | CA7 intr mask[1] | CA7 interrupt mask register1 |

0x9C0007DC | G15.23 | CA7 intr mask[2] | CA7 interrupt mask register2 |

0x9C0007E0 | G15.24 | CA7 intr mask[3] | CA7 interrupt mask register3 |

0x9C0007E4 | G15.25 | CA7 intr mask[4] | CA7 interrupt mask register4 |

0x9C0007E8 | G15.26 | CA7 intr mask[5] | CA7 interrupt mask register5 |

0x9C0007EC | G15.27 | CA7 intr mask[6] | CA7 interrupt mask register6 |

0x9C0007F0 | G15.28 | rsv | Reserve |

0x9C0007F4 | G15.29 | rsv | Reserve |

0x9C0007F8 | G15.30 | rsv | Reserve |

0x9C0007FC | G15.31 | rsv | Reserve |

Address | Group No. | Register Name | Description |

|---|---|---|---|

0x9C000A80 | G21.0 | CA7 intr clr[0] | CA7 interrupt clear register0 |

0x9C000A84 | G21.1 | CA7 intr clr[1] | CA7 interrupt clear register1 |

0x9C000A88 | G21.2 | CA7 intr clr[2] | CA7 interrupt clear register2 |

0x9C000A8C | G21.3 | CA7 intr clr[3] | CA7 interrupt clear register3 |

0x9C000A90 | G21.4 | CA7 intr clr[4] | CA7 interrupt clear register4 |

0x9C000A94 | G21.5 | CA7 intr clr[5] | CA7 interrupt clear register5 |

0x9C000A98 | G21.6 | CA7 intr clr[6] | CA7 interrupt clear register6 |

0x9C000A9C | G21.7 | masked CA7 fiqs[0] | Masked CA7 FIQ register0 |

0x9C000AA0 | G21.8 | masked CA7 fiqs[1] | Masked CA7 FIQ register1 |

0x9C000AA4 | G21.9 | masked CA7 fiqs[2] | Masked CA7 FIQ register2 |

0x9C000AA8 | G21.10 | masked CA7 fiqs[3] | Masked CA7 FIQ register3 |

0x9C000AAC | G21.11 | masked CA7 fiqs[4] | Masked CA7 FIQ register4 |

0x9C000AB0 | G21.12 | masked CA7 fiqs[5] | Masked CA7 FIQ register5 |

0x9C000AB4 | G21.13 | masked CA7 fiqs[6] | Masked CA7 FIQ register6 |

0x9C000AB8 | G21.14 | masked CA7 irqs[0] | Masked CA7 IRQ register0 |

0x9C000ABC | G21.15 | masked CA7 irqs[0] | Masked CA7 IRQ register1 |

0x9C000AC0 | G21.16 | masked CA7 irqs[0] | Masked CA7 IRQ register2 |

0x9C000AC4 | G21.17 | masked CA7 irqs[0] | Masked CA7 IRQ register3 |

0x9C000AC8 | G21.18 | masked CA7 irqs[0] | Masked CA7 IRQ register4 |

0x9C000ACC | G21.19 | masked CA7 irqs[5] | Masked CA7 IRQ register5 |

0x9C000AD0 | G21.20 | masked CA7 irqs[6] | Masked CA7 IRQ register6 |

0x9C000AD4 | G21.21 | rsv | Reserve |

0x9C000AD8 | G21.22 | rsv | Reserve |

0x9C000ADC | G21.23 | rsv | Reserve |

0x9C000AE0 | G21.24 | rsv | Reserve |

0x9C000AE4 | G21.25 | rsv | Reserve |

0x9C000AE8 | G21.26 | rsv | Reserve |

0x9C000AEC | G21.27 | rsv | Reserve |

0x9C000AF0 | G21.28 | rsv | Reserve |

0x9C000AF4 | G21.29 | rsv | Reserve |

0x9C000AF8 | G21.30 | rsv | Reserve |

0x9C000AFC | G21.31 | intr group | Interrupt group register |

9.7.2 Registers Description

RGST Table Group 15 INTERRUPT 2

15.0 Interrupt type register0 (intr type[0])

Address: 0x9C000780

Reset: 0x8000 025F

| Field Name | Bit | Access | Description |

| intr type[31:0] | 31:0 | RW | Determine interrupt type from bit 0 to 31 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.1 Interrupt type register1 (intr type[1])

Address: 0x9C000784

Reset: 0x0800 0004

| Field Name | Bit | Access | Description |

| intr type[63:32] | 31:0 | RW | Determine interrupt type from bit 32 to 63 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.2 Interrupt type register2 (intr type[2])

Address: 0x9C000788

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| intr type[95:64] | 31:0 | RW | Determine interrupt type from bit 64 to 95 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.3 Interrupt type register3 (intr type[3])

Address: 0x9C00078C

Reset: 0x0003 C000

| Field Name | Bit | Access | Description |

| intr type[127:96] | 31:0 | RW | Determine interrupt type from bit 96 to 127 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.4 Interrupt type register4 (intr type[4])

Address: 0x9C000790

Reset: 0xFF80 0000

| Field Name | Bit | Access | Description |

| intr type[159:128] | 31:0 | RW | Determine interrupt type from bit 128 to 159 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.5 Interrupt type register5 (intr type[5])

Address: 0x9C000794

Reset: 0xFFC0 00FF

| Field Name | Bit | Access | Description |

| intr type[191:160] | 31:0 | RW | Determine interrupt type from bit 160 to 191 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.6 Interrupt type register6 (intr type[6])

Address: 0x9C000798

Reset: 0x0000 00FF

| Field Name | Bit | Access | Description |

| Reserve | 31:8 | RO | |

| intr type[199:192] | 7:0 | RW | Determine interrupt type from bit 192 to 199 Different interrupt source has different default value. 0: level-type 1: edge-type |

15.7 Interrupt polarity register0 (intr polarity[0])

Address: 0x9C00079C

Reset: 0x0000 00FF

| Field Name | Bit | Access | Description |

| intr polarity[31:0] | 31:0 | RW | Determine interrupt polarity from bit 0 to 31 0: high-active(default) 1: low-active |

15.8 Interrupt polarity register1 (intr polarity[1])

Address: 0x9C0007A0

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| intr polarity[63:32] | 31:0 | RW | Determine interrupt polarity from bit 32 to 63 0: high-active(default) 1: low-active |

15.9 Interrupt polarity register2 (intr polarity[2])

Address:0x9C0007A4

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| intr polarity[95:64] | 31:0 | RW | Determine interrupt polarity from bit 64 to 95 0: high-active(default) 1: low-active |

15.10 Interrupt polarity register3 (intr polarity[3])

Address:0x9C0007A8

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| intr polarity[127:96] | 31:0 | RW | Determine interrupt polarity from bit 96 to 127 0: high-active(default) 1: low-active |

15.11Interrupt polarity register4 (intr polarity[4])

Address:0x9C0007AC

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| intr polarity[159:128] | 31:0 | RW | Determine interrupt polarity from bit 128 to 159 0: high-active(default) 1: low-active |

15.12 Interrupt polarity register5 (intr polarity[5])

Address: 0x9C0007B0

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| intr polarity[191:160] | 31:0 | RW | Determine interrupt polarity from bit 160 to 191 0: high-active(default) 1: low-active |

15.13 Interrupt polarity register6 (intr polarity[6])

Address: 0x9C0007B4

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserve | 31:8 | RO | |

| intr polarity[199:192] | 7:0 | RW | Determine interrupt polarity from bit 192 to 199 0: high-active(default) 1: low-active |

15.14 CA7 priority register0 (CA7 priority[0])

Address: 0x9C0007B8

Reset:0xffff ffff

| Field Name | Bit | Access | Description |

| CA7 priority[31:0] | 31:0 | RW | Determine CA7 interrupt priority from bit 0 to 31 0: fiq(default) 1: irq |

15.15 CA7 priority register1 (CA7 priority[1])

Address: 0x9C0007BC

Reset: 0xffff ffff

| Field Name | Bit | Access | Description |

| CA7 priority[63:32] | 31:0 | RW | Determine CA7 interrupt priority from bit 32 to 63 0: fiq(default) 1: irq |

15.16 CA7 priority register2 (CA7 priority[2])

Address: 0x9C0007C0

Reset:0xffff ffff

| Field Name | Bit | Access | Description |

| CA7 priority[95:64] | 31:0 | RW | Determine CA7 interrupt priority from bit 64 to 95 0: fiq(default) 1: irq |

15.17 CA7 priority register3 (CA7 priority[3])

Address: 0x9C0007C4

Reset: 0xffff ffff

| Field Name | Bit | Access | Description |

| CA7 priority[127:96] | 31:0 | RW | Determine CA7 interrupt priority from bit 96 to 127 0: fiq(default) 1: irq |

15.18 CA7 priority register4 (CA7 priority[4])

Address: 0x9C0007C8

Reset: 0xffff ffff

| Field Name | Bit | Access | Description |

| CA7 priority[159:128] | 31:0 | RW | Determine CA7 interrupt priority from bit 128 to 159 0: fiq(default) 1: irq |

15.19 CA7 priority register5 (CA7 priority[5])

Address: 0x9C0007CC

Reset: 0xffff ffff

| Field Name | Bit | Access | Description |

| CA7 priority[191:160] | 31:0 | RW | Determine CA7 interrupt priority from bit 160 to 191 0: fiq(default) 1: irq |

15.20 CA7 priority register6 (CA7 priority[6])

Address: 0x9C0007D0

Reset: 0x0000 00ff

| Field Name | Bit | Access | Description |

| Reserve | 31:8 | RO | |

| CA7 priority[199:192] | 7:0 | RW | Determine CA7 interrupt priority from bit 192 to 199 0: fiq(default) 1: irq |

15.21 CA7 interrupt mask register0 (CA7 intr mask[0])

Address: 0x9C0007D4

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| CA7 intr mask[31:0] | 31:0 | RW | Mask CA7 interrupt from bit 0 to 31 0: masked(default) 1: pass |

15.22 CA7 interrupt mask register1 (CA7 intr mask[1])

Address: 0x9C0007D8

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| CA7 intr mask[63:32] | 31:0 | RW | Mask CA7 interrupt from bit 32 to 63 0: masked(default) 1: pass |

15.23 CA7 interrupt mask register2 (CA7 intr mask[2])

Address: 0x9C0007DC

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| CA7 intr mask[95:64] | 31:0 | RW | Mask CA7 interrupt from bit 64 to 95 0: masked(default) 1: pass |

15.24 CA7 interrupt mask register3 (CA7 intr mask[3])

Address: 0x9C0007E0

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| CA7 intr mask[127:96] | 31:0 | RW | Mask CA7 interrupt from bit 96 to 127 0: masked(default) 1: pass |

15.25 CA7 interrupt mask register4 (CA7 intr mask[4])

Address: 0x9C0007E4

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| CA7 intr mask[159:128] | 31:0 | RW | Mask CA7 interrupt from bit 128 to 159 0: masked(default) 1: pass |

15.26 CA7 interrupt mask register5 (CA7 intr mask[5])

Address: 0x9C0007E8

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| CA7 intr mask[191:160] | 31:0 | RW | Mask CA7 interrupt from bit 160 to 191 0: masked(default) 1: pass |

15.27 CA7 interrupt mask register6 (CA7 intr mask[6])

Address: 0x9C0007EC

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Reserve | 31:8 | RO | |

| CA7 intr mask[199:192] | 7:0 | RW | Mask CA7 interrupt from bit 192 to 199 0: masked(default) 1: pass |

15.28 Reserve (rsv)

Address: 0x9C0007F0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | RO |

15.29 Reserve (rsv)

Address: 0x9C0007F4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | RO |

15.30 Reserve (rsv)

Address: 0x9C0007F8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | RO |

15.31 Reserve (rsv)

Address: 0x9C0007FC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| Reserve | 31:1 | RO | Reserve |

| Reserve | 0 | RW | Reserve |

RGST Table Group 21 INTERRUPT 3

21.0 CA7 interrupt clear register0 (CA7 intr clr[0])

Address: 0x9C000A80

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| CA7 intr clr[31:0] | 31:0 | WO | Clear CA7 interrupt from bit 0 to 31 |

21.1 CA7 interrupt clear register1 (CA7 intr clr[1])

Address: 0x9C000A84

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| CA7 intr clr[63:32] | 31:0 | WO | Clear CA7 interrupt from bit 32 to 63 |

21.2 CA7 interrupt clear register2 (CA7 intr clr[2])

Address: 0x9C000A88

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| CA7 intr clr[95:64] | 31:0 | WO | Clear CA7 interrupt from bit 64 to 95 |

21.3 CA7 interrupt clear register3 (CA7 intr clr[3])

Address: 0x9C000A8C

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| CA7 intr clr[127:96] | 31:0 | WO | Clear CA7 interrupt from bit 96 to 127 |

21.4 CA7 interrupt clear register4 (CA7 intr clr[4])

Address: 0x9C000A90

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| CA7 intr clr[159:128] | 31:0 | WO | Clear CA7 interrupt from bit 128 to 159 |

21.5 CA7 interrupt clear register5 (CA7 intr clr[5])

Address: 0x9C000A94

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| CA7 intr clr[191:160] | 31:0 | WO | Clear CA7 interrupt from bit 160 to 191 |

21.6 CA7 interrupt clear register6 (CA7 intr clr[6])

Address: 0x9C000A98

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:8 | WO | Reserve |

| CA7 intr clr[199:192] | 7:0 | WO | Clear CA7 interrupt from bit 192 to 199 |

21.7 Masked CA7 FIQ register0 (masked CA7 fiqs[0])

Address: 0x9C000A9C

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7fiqs[31:0] | 31:0 | RO | Read masked CA7 fiqs from bit 0 to 31 |

21.8 Masked CA7 FIQ register1 (masked CA7 fiqs[1])

Address: 0x9C000AA0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 fiqs[63:32] | 31:0 | RO | Read masked CA7 fiqs from bit 32 to 63 |

21.9 Masked CA7 FIQ register2 (masked CA7 fiqs[2])

Address: 0x9C000AA4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 fiqs[95:64] | 31:0 | RO | Read masked CA7 fiqs from bit 64 to 95 |

21.10 Masked CA7 FIQ register3 (masked CA7 fiqs[3])

Address: 0x9C000AA8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 fiqs[127:96] | 31:0 | RO | Read masked CA7 fiqs from bit 96 to 127 |

21.11 Masked CA7 FIQ register4 (masked CA7 fiqs[4])

Address: 0x9C000AAC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 fiqs[159:128] | 31:0 | RO | Read masked CA7 fiqs from bit 128 to 159 |

21.12 Masked CA7 FIQ register5 (masked CA7 fiqs[5])

Address: 0x9C000AB0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 fiqs[191:160] | 31:0 | RO | Read masked CA7 fiqs from bit 160 to 191 |

21.13 Masked CA7 FIQ register6 (masked CA7 fiqs[6])

Address: 0x9C000AB4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:8 | RO | Reserve |

| masked CA7 fiqs[199:192] | 7:0 | RO | Read masked CA7 fiqs from bit 192 to 199 |

21.14 Masked CA7 IRQ register0 (masked CA7 irqs[0])

Address: 0x9C000AB8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 irqs[31:0] | 31:0 | RO | Read masked CA7 irqs from bit 0 to 31 |

21.15 Masked CA7 IRQ register1 (masked CA7 irqs[1])

Address: 0x9C000ABC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 irqs[63:32] | 31:0 | RO | Read masked CA7 irqs from bit 32 to 63 |

21.16 Masked CA7 IRQ register2 (masked CA7 irqs[2])

Address: 0x9C000AC0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 irqs[95:64] | 31:0 | RO | Read masked CA7 irqs from bit 64 to 95 |

21.17 Masked CA7 IRQ register3 (masked CA7 irqs[3])

Address: 0x9C000AC4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 irqs[127:96] | 31:0 | RO | Read masked CA7 irqs from bit 96 to 127 |

21.18 Masked CA7 IRQ register4 (masked CA7 irqs[4])

Address: 0x9C000AC8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 irqs[159:128] | 31:0 | RO | Read masked CA7 irqs from bit 128 to 159 |

21.19 Masked CA7 IRQ register5 (masked CA7 irqs[5])

Address: 0x9C000ACC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| masked CA7 irqs[191:160] | 31:0 | RO | Read masked CA7 irqs from bit 160 to 191 |

21.20 Masked CA7 IRQ register6 (masked CA7 irqs[6])

Address: 0x9C000AD0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:8 | RO | Reserve |

| masked CA7 irqs[199:192] | 7:0 | RO | Read masked CA7 irqs from bit 192 to 199 |

21.21 Reserve (rsv)

Address: 0x9C000AD4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.22 Reserve (rsv)

Address: 0x9C000AD8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.23 Reserve (rsv)

Address: 0x9C000ADC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.24 Reserve (rsv)

Address: 0x9C000AE0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.25 Reserve (rsv)

Address: 0x9C000AE4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.26 Reserve (rsv)

Address: 0x9C000AE8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.27 Reserve (rsv)

Address: 0x9C000AEC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.28 Reserve (rsv)

Address: 0x9C000AF0

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.29 Reserve (rsv)

Address: 0x9C000AF4

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | WO |

21.30 Reserve (rsv)

Address:0x9C000AF8

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

Reserve | 31:0 | RO |

21.31 Interrupt group register (intr group)

Address: 0x9C000AFC

Reset: 0x0000 0000

Field Name | Bit | Access | Description |

| Reserve | 31:23 | RO | |

| dsp intr group[6:0] | 22:16 | RO | Which interrupt group is triggered for DSP bit16: masked dsp intr[31:0] bit17: masked dsp intr[63:32] bit18: masked dsp intr[95:64] bit19: masked dsp intr[127:96] bit20: masked dsp intr[159:128] bit21: masked dsp intr[191:160] bit22: masked dsp intr[199:192] |

| Reserve | 15 | RO | |

| a926 irq group[6:0] | 14:8 | RO | Which interrupt group is triggered for ARM926 IRQ bit8: masked a926 irq[31:0] bit9: masked a926 irq[63:32] bit10: masked a926 irq[95:64] bit11: masked a926 irq[127:96] bit12: masked a926 irq[159:128] bit13: masked a926 irq[191:160] bit14: masked a926 irq[199:192] |

| Reserve | 7 | RO | |

| a926 fiq group[6:0] | 6:0 | RO | Which interrupt group is triggered for ARM926 FIQ bit0: masked a926 fiq[31:0] bit1: masked a926 fiq[63:32] bit2: masked a926 fiq[95:64] bit3: masked a926 fiq[127:96] bit4: masked a926 fiq[159:128] bit5: masked a926 fiq[191:160] bit6: masked a926 fiq[199:192] |