7. System Control

7.1 Introduction

This chapter will introduce the basic system control registers. For example, the clock and reset enable/disable of each block, the pinmux select, the thermal control, the DC2DC control and the GPIO select control. It can help user to set basic parameters for system and flexible operations. This chapter describes the following information and functions. (Detail descriptions please check each register list)

- Group 0: Describe the parameters of each block clock and reset enable/disable.

- Group 1: Describe the pinmux parameters.

- Group 2: Describe the pinmux parameters.

- Group 3: Describe the pinmux parameters.

- Group 4: Describe the PLL setting parameters for each block.

- Group 5: Describe the thermal and DC2DC control parameters.

- Group 6: Describe the GPIO control parameters.

- Group 7: Describe the GPIO control parameters.

7.2 Hardware Reset control

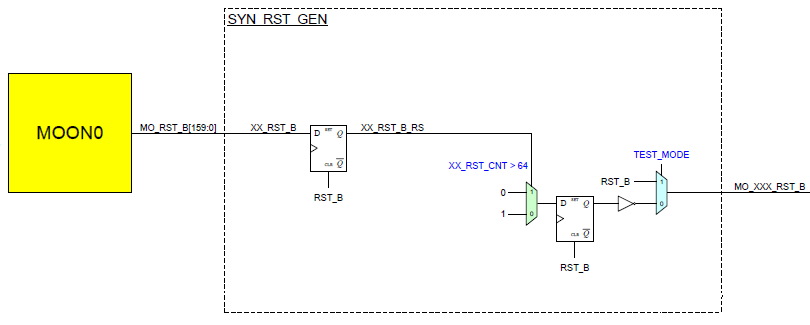

The system blocks reset can be issued by the Group0.21~30 registers. Each bit map to correspond block. Please make sure the reset bit set as 0 when the block starts to work.For example, if user want to enable I2CM0 reset, please set 0x00010001 to Group0.24 register. Set 0x00010000 to Group0.24 to disable reset.Figure 7-1 show the system hardware reset generator. Moon0 block mean Group0 registers that include control bits in lower 16bits and mask bits in higher 16bits.

Figure 7-1 Hardware Reset Generator

7.3 Clock enable control

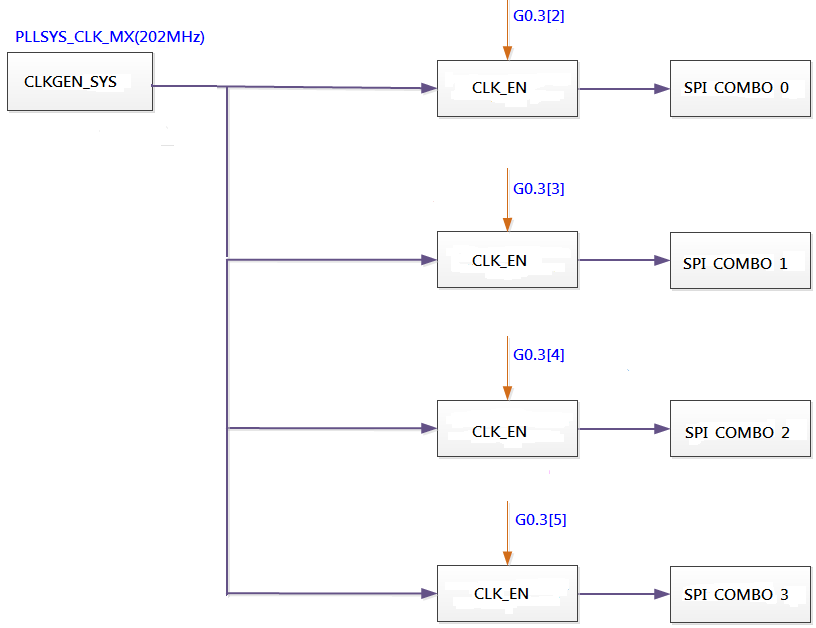

The system blocks clock can be enabled or disabled by the Group0.1~10 registers. Each bit map to correspond block. Please set the clock bit to 1 for enable the block's clock.For example, if user want to enable SPI_COMBO_0 clock, please set 0x00040004 to Group0.3 register. Set 0x00040000 to Group0.3 to disable clock.Figure 7-2 show the SPI_COMBO block clock enable structure.

Figure 7-2 SPI_COMBO Block Clock Enable

7.4 System PLL control

There are 5 system PLL blocks in SP7021, they are PLLSYS, PLLA, PLLE, PLLF and PLLTV. They can be programmable by the Group4.0~16 registers.

7.4.1 PLLSYS control

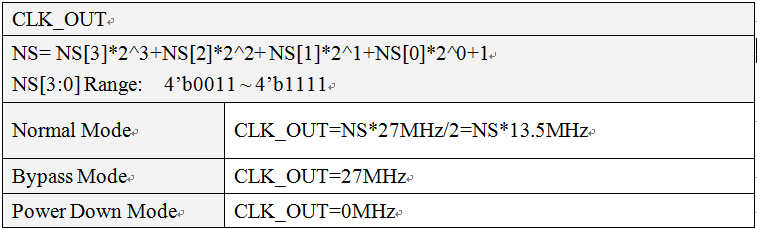

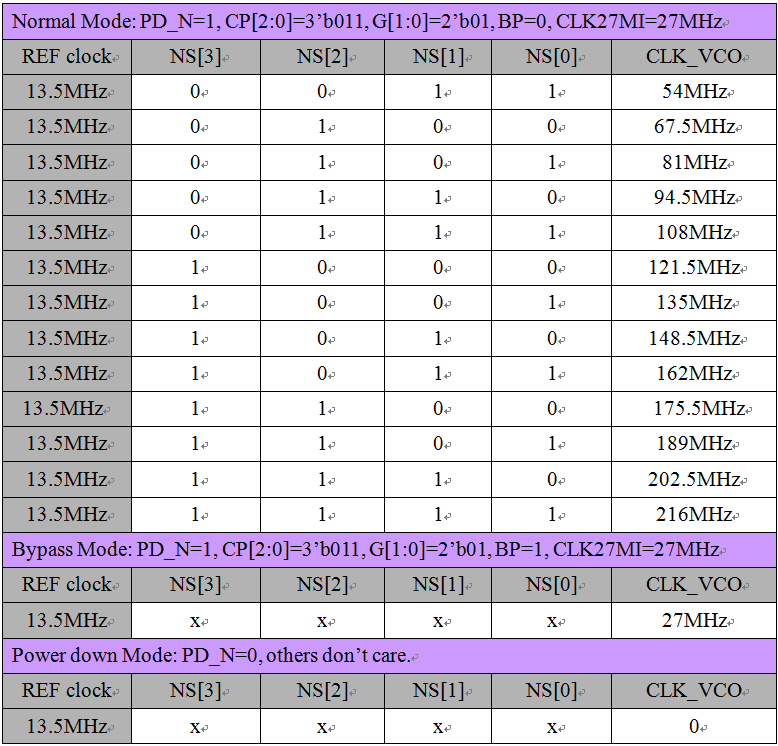

The PLLSYS is used for generating system clock; it could generate wide frequency range with different register setting, Also the PLLSYS could operate steady with low time jitter and low power consumption. The control register is Group4.26. There are three mode in PLLSYS module. Please refer to table 7-1&7-2 for parameters setting.

Table 7-1 Three mode PLLSYS

Table 7-2 The detail setting of three mode PLLSYS

7.4.2 PLLF control

The PLLFLASH(PLLF) is mainly used as clock sources for eMMC, SPI-NAND or SPI-NOR Flash memory. It could generate wide frequency range with different register setting, Also the PLLFLASH could operate steady with low time jitter and low power consumption. The control register is Group4.13. PLLSYS & PLLFLASH have identical function structure so each control bit usage is the same. Please refer to table 7-1&7-2 for parameters setting.

7.4.3 PLLE control

The PLLE is mainly used as clock source for ethernet. It could generate 4 kinds frequency, 50MHz, 2.5MHz, 25MHz and 112.5MHz, which controlled by register Group4.12 bit14, 13, 12 and 11. Please refer to Group4.12 register for detail parameters setting.

7.4.4 PLLTV control

The PLLTV is mainly used as clock source for HDMITX and Display module. It could generate wide frequency range with different register setting, Also the PLLTV could operate steady with low time jitter and low power consumption. The control registers are Group4.14, 15 and 16.

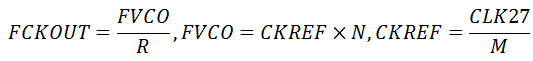

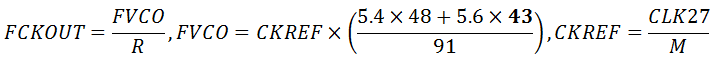

Frequency Operate Equation:

- Integer MODE (SEL_FRA_TV=0)

(A) DIVM [6:0]: Reference divider

Ex. M=1 for DIVM[6:0]=7’b000_0000, M=32 for DIVM[6:0]=7’b001_1111.

(B) DIVN [7:0]: PLL feedback divider

Ex. N=11 for DIVN[7:0]=8’b0000_1010, N=32 for DIVN[7:0]=8’b0001_1111.

(C) DIVR[1:0]: Post divider

Ex. R=0 for Divisor=1: FCKOUT= FVCO / 1

R=1 for Divisor=2: FCKOUT= FVCO / 2

R=2 for Divisor=4: FCKOUT= FVCO / 4

R=3 for Divisor=8: FCKOUT= FVCO / 8

- Fractional MODE (SEL_FRA_TV=1, DOUBLE_SEL_TV=0)

- For SDM_MOD_TV=0, PH_SEL_TV=0, NFRA=45

- For SDM_MOD_TV=0, PH_SEL_TV=1, NFRA=43

(A) DIVN [7:0]: PLL feedback divider is useless

DIVM & DIVR are the same as Integer mode

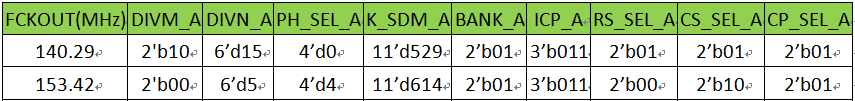

7.4.5 PLLA control

The PLLA is mainly used as clock source for audio module. It could generate wide frequency range with different register setting, Also the PLLA could operate steady with low time jitter and low power consumption. The control registers are Group4.7~11.

Frequency Operate Equation:

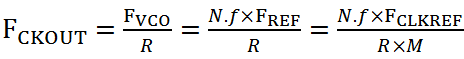

where R is modulus set by DIVR_A and M by DIVM_A.

FCKOUT indicates frequency of FCKOUT_A, FVCO stands for the frequency of VCO and FCLKREF is the frequency of CLKREF_A(27MHz).

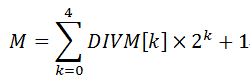

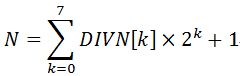

- Fractional dividing modulus of f

where N.fideal is an ideal fractional dividing modulus and N.fbase is the basic fractional dividing modulus controlled by DIVN_A & PH_SEL_A.

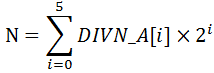

DIVN_A directly represent integer part of the basic fractional dividing modulus shown below:

It should be noted that exception for N cannot be set less than 2 .

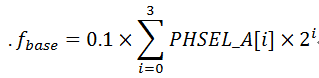

The N.fbase provides user a basic fractional dividing modulus with resolution of multiple of 0.1, and the fractional part is controlled by PH_SEL_A as shown in the pin description section. User can intuitively set this part:

It should be noted that exception for .fbase is that setting PH_SEL_A=4’b1001~4’b1110 makes N.fideal a truly integer dividing modulus “plus one”, regardless of K & M.

For example, DIVN_A=6’b000100 and PH_SEL_A=4’b1001 makes N.fideal=4+1=5

The last part is the residue of the fractional dividing modulus, the ratio of K to M, which is realized by PH_STEP_SEL_A, M_SDM_A & K_SDM_A. Both K & M can be arbitrarily set from 0~2047 and noted that K must be equal or less than M, and the coefficient of 0.1 is set by PH_STEP_SEL=2’b01.

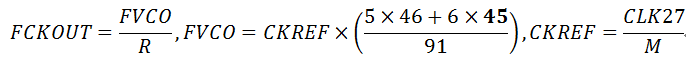

Now user can try to randomly give a fractional dividing modulus. There has an examples shown below.

Ex: N.f = 5.4033333 = 5+0.4+0.01x341/1023

DIVN_A=6’b000101, PH_SEL_A=4’b0100, PH_STEP_SEL=2’b01, K_SDM_A=11’b001-0101-0101 and M_SDM_A=11’b011-1111-1111

- Frequency calculate example

M_SDM_A=11’b1001, DIVR_A=2’b00, DOUBLE_SEL=1’b0, MUX_SEL_A=1’b0, PH_STEP_SEL_A=2’b01

7.5 DC2DC control

SP7021 embedded 3 DC2DC modules, they are 3.3V to 0.9V, 3.3V to 1.2V and 3.3V to 1.5V. So SP7021 just need one single power supply that is 3.3V. The parameters can be set by Group5.23~31 registers.

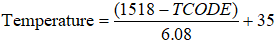

7.6 Thermal sensor control

SP7021 embedded a thermal sensor which operation temperature range between -40°C ~125°C. The resolution is 1°C. The parameters can be set by Group5 registers.

For example, when MO_THERMAL_VBE_SEL=0x01(default), then read TCODE value from G5.12[10:0] and calculate chip temperature as below:

Unit is Celsius.

7.7 System Pinmux control

There are totally 64 pins can be set as Multiplex Peripheral Pins. Multiplex Peripheral Pins include ETH_SW, SDIO, PWM, Input Capture, SPI MASTER, SPI SLAVE, I2C MASTER, UART(1~4), TIMER, GPIO INT functions. This function can be controlled by Group2~3 registers. Please refer to chapter 5 for detail description of this function.

Another pinmux type which provide fixed function in fixed pins is also supported. They can be control by Group1.1~4 registers. For example, in the chapter 4 pin description, the pin92~97 describe as below:

| Pin Name | LQFP 176 Pin No | Type | Description(Multiplex Pins in this interface Shown in Bold) | Drive (mA) |

|---|---|---|---|---|

EMMC_D0/ SPI_NAND_D0 | 92 | I/O I/O | EMMC data pin0 SPI_NAND_D0 | |

EMMC_D1/ SPI_NAND_D2 | 93 | I/O I/O | EMMC data pin1 SPI_NAND_D2 | |

EMMC_CLK/ SPI_NAND_CLK | 94 | I/O I/O | EMMC clock pin SPI_NAND_CLK | |

EMMC_D2/ SPI_NAND_D1 | 95 | I/O I/O | EMMC data pin2 SPI_NAND_D1 | |

EMMC_D7/ SPI_NAND_D3 | 96 | I/O I/O | EMMC data pin7 SPI_NAND_D3 | |

EMMC_D6/ SPI_NAND_CEN | 97 | I/O I/O | EMMC data pin6 SPI_NAND_CEN |

If user set Group1.1[4] as "1", the pin92~97 will support SPI_NAND function interface.

If user set Group1.1[5] as "1". the pin92~97 will become EMMC function interface.

7.8 System GPIO control

There are totally 72 GPIO pins which are separated into 9 I/O ports, and each port contains 8 GPIO signals. The I/O driving capability for signals in GPIO0 is 16mA and 8mA for those in other GPIO ports. All 72 GPIO signals are Tri-state Output with Schmitt Trigger Input. The GPIO can be controlled by Group6~7 registers. Please refer to chapter 5 for detail description of this function.

7.9 Core Clock Divide Enable

There has a special mode to divide core clock to half. Core clock is generated by dividing pll clock, so set pll cleck to half, it will let core clock become half also. The control bit is CORECLK_DIV2_EN which map to 0x9EC0000C[10]. 0: Pll cleck, 1: Pll clock/2.

7.10 Registers Map

7.10.1 Registers Memory Map

Address | Group No. | Register Name | Register Description |

0x9C000000 | G0.0 | mo stamp | Chip Revision Stamp ID Register |

0x9C000004 | G0.1 | mo clken0 | Clock Enable Register #0 |

0x9C000008 | G0.2 | mo clken1 | Clock Enable Register #1 |

0x9C00000C | G0.3 | mo clken2 | Clock Enable Register #2 |

0x9C000010 | G0.4 | mo clken3 | Clock Enable Register #3 |

0x9C000014 | G0.5 | mo clken4 | Clock Enable Register #4 |

0x9C000018 | G0.6 | mo clken5 | Clock Enable Register #5 |

0x9C00001C | G0.7 | mo clken6 | Clock Enable Register #6 |

0x9C000020 | G0.8 | mo clken7 | Clock Enable Register #7 |

0x9C000024 | G0.9 | mo clken8 | Clock Enable Register #8 |

0x9C000028 | G0.10 | mo clken9 | Clock Enable Register #9 |

0x9C00002C | G0.11 | mo gclken0 | Clock Gating Enable Register #0 |

0x9C000030 | G0.12 | mo gclken1 | Clock Gating Enable Register #1 |

0x9C000034 | G0.13 | mo gclken2 | Clock Gating Enable Register #2 |

0x9C000038 | G0.14 | mo gclken3 | Clock Gating Enable Register #3 |

0x9C00003C | G0.15 | mo gclken4 | Clock Gating Enable Register #4 |

0x9C000040 | G0.16 | mo gclken5 | Clock Gating Enable Register #5 |

0x9C000044 | G0.17 | mo gclken6 | Clock Gating Enable Register #6 |

0x9C000048 | G0.18 | mo gclken7 | Clock Gating Enable Register #7 |

0x9C00004C | G0.19 | mo gclken8 | Clock Gating Enable Register #8 |

0x9C000050 | G0.20 | mo gclken9 | Clock Gating Enable Register #9 |

0x9C000054 | G0.21 | mo reset0 | Hardware Reset Control Register #0 |

0x9C000058 | G0.22 | mo reset1 | Hardware Reset Control Register #1 |

0x9C00005C | G0.23 | mo reset2 | Hardware Reset Control Register #2 |

0x9C000060 | G0.24 | mo reset3 | Hardware Reset Control Register #3 |

0x9C000064 | G0.25 | mo reset4 | Hardware Reset Control Register #4 |

0x9C000068 | G0.26 | mo reset5 | Hardware Reset Control Register #5 |

0x9C00006C | G0.27 | mo reset6 | Hardware Reset Control Register #6 |

0x9C000070 | G0.28 | mo reset7 | Hardware Reset Control Register #7 |

0x9C000074 | G0.29 | mo reset8 | Hardware Reset Control Register #8 |

0x9C000078 | G0.30 | mo reset9 | Hardware Reset Control Register #9 |

0x9C00007C | G0.31 | mo sft cfg mode | Software Configure Hardware Mode |

Address | Group No. | Register Name | Register Description |

0x9C000080 | G1.0 | sft cfg 0 | Test Mode Control Register |

0x9C000084 | G1.1 | sft cfg 1 | PIN Mux Table Control Register #1 |

0x9C000088 | G1.2 | sft cfg 2 | PIN Mux Table Control Register #2 |

0x9C00008C | G1.3 | sft cfg 3 | PIN Mux Table Control Register #3 |

0x9C000090 | G1.4 | sft cfg 4 | PIN Mux Table Control Register #4 |

0x9C000094 | G1.5 | rsv | Reserved |

0x9C000098 | G1.6 | rsv | Reserved |

0x9C00009C | G1.7 | rsv | Reserved |

0x9C0000A0 | G1.8 | rsv | Reserved |

0x9C0000A4 | G1.9 | rsv | Reserved |

0x9C0000A8 | G1.10 | rsv | Reserved |

0x9C0000AC | G1.11 | rsv | Reserved |

0x9C0000B0 | G1.12 | rsv | Reserved |

0x9C0000B4 | G1.13 | rsv | Reserved |

0x9C0000B8 | G1.14 | rsv | Reserved |

0x9C0000BC | G1.15 | rsv | Reserved |

0x9C0000C0 | G1.16 | rsv | Reserved |

0x9C0000C4 | G1.17 | rsv | Reserved |

0x9C0000C8 | G1.18 | rsv | Reserved |

0x9C0000CC | G1.19 | rsv | Reserved |

0x9C0000D0 | G1.20 | rsv | Reserved |

0x9C0000D4 | G1.21 | rsv | Reserved |

0x9C0000D8 | G1.22 | rsv | Reserved |

0x9C0000DC | G1.23 | rsv | Reserved |

0x9C0000E0 | G1.24 | rsv | Reserved |

0x9C0000E4 | G1.25 | rsv | Reserved |

0x9C0000E8 | G1.26 | rsv | Reserved |

0x9C0000EC | G1.27 | rsv | Reserved |

0x9C0000F0 | G1.28 | rsv | Reserved |

0x9C0000F4 | G1.29 | rsv | Reserved |

0x9C0000F8 | G1.30 | rsv | Reserved |

0x9C0000FC | G1.31 | rsv | Reserved |

Address | Group No. | Register Name | Register Description |

0x9C000100 | G2.0 | sft cfg 0 | PIN Mux Table Control Register for L2SW CLK & L2SW LED |

0x9C000104 | G2.1 | sft cfg 1 | PIN Mux Table Control Register for L2SW LED & L2SW LED |

0x9C000108 | G2.2 | sft cfg 2 | PIN Mux Table Control Register for L2SW LED & L2SW MAC |

0x9C00010C | G2.3 | sft cfg 3 | PIN Mux Table Control Register for L2SW P0 & L2SW P0 |

0x9C000110 | G2.4 | sft cfg 4 | PIN Mux Table Control Register for L2SW P0 & L2SW P0 |

0x9C000114 | G2.5 | sft cfg 5 | PIN Mux Table Control Register for L2SW P0 & L2SW P0 |

0x9C000118 | G2.6 | sft cfg 6 | PIN Mux Table Control Register for L2SW P0 & L2SW P1 |

0x9C00011C | G2.7 | sft cfg 7 | PIN Mux Table Control Register for L2SW P1 & L2SW P1 |

0x9C000120 | G2.8 | sft cfg 8 | PIN Mux Table Control Register for L2SW P1 & L2SW P1 |

0x9C000124 | G2.9 | sft cfg 9 | PIN Mux Table Control Register for L2SW P1 & L2SW P1 |

0x9C000128 | G2.10 | sft cfg 10 | PIN Mux Table Control Register for L2SW P1 & DAISY MODE |

0x9C00012C | G2.11 | sft cfg 11 | PIN Mux Table Control Register for SDIO CLK & SDIO CMD |

0x9C000130 | G2.12 | sft cfg 12 | PIN Mux Table Control Register for SDIO D0 & SDIO D1 |

0x9C000134 | G2.13 | sft cfg 13 | PIN Mux Table Control Register for SDIO D2 & SDIO D3 |

0x9C000138 | G2.14 | sft cfg 14 | PIN Mux Table Control Register for PWM0 & PWM1 |

0x9C00013C | G2.15 | sft cfg 15 | PIN Mux Table Control Register for PWM2 & PWM3 |

0x9C000140 | G2.16 | sft cfg 16 | PIN Mux Table Control Register for PWM4 & PWM5 |

0x9C000144 | G2.17 | sft cfg 17 | PIN Mux Table Control Register for PWM6 & PWM7 |

0x9C000148 | G2.18 | sft cfg 18 | PIN Mux Table Control Register for ICM0 D & ICM1 D |

0x9C00014C | G2.19 | sft cfg 19 | PIN Mux Table Control Register for ICM2 D & ICM3 D |

0x9C000150 | G2.20 | sft cfg 20 | PIN Mux Table Control Register for ICM0 CLK & ICM1 CLK |

0x9C000154 | G2.21 | sft cfg 21 | PIN Mux Table Control Register for ICM2 CLK & ICM3 CLK |

0x9C000158 | G2.22 | sft cfg 22 | PIN Mux Table Control Register for SPIM0 INT & SPIM0 CLK |

0x9C00015C | G2.23 | sft cfg 23 | PIN Mux Table Control Register for SPIM0 EN & SPIM0 DO |

0x9C000160 | G2.24 | sft cfg 24 | PIN Mux Table Control Register for SPIM0 DI & SPIM1 INT |

0x9C000164 | G2.25 | sft cfg 25 | PIN Mux Table Control Register for SPIM1 CLK & SPIM1 CEN |

0x9C000168 | G2.26 | sft cfg 26 | PIN Mux Table Control Register for SPIM1 DO & SPIM1 DI |

0x9C00016C | G2.27 | sft cfg 27 | PIN Mux Table Control Register for SPIM2 INT |

0x9C000170 | G2.28 | sft cfg 28 | PIN Mux Table Control Register for SPIM2 CEN & SPIM2 DO |

0x9C000174 | G2.29 | sft cfg 29 | PIN Mux Table Control Register for SPIM2 DI & SPIM3 INT |

0x9C000178 | G2.30 | sft cfg 30 | PIN Mux Table Control Register for SPIM3 CLK & SPIM3 CEN |

0x9C00017C | G2.31 | sft cfg 31 | PIN Mux Table Control Register for SPIM3 DO & SPIM3 DI |

Address | Group No. | Register Name | Register Description |

0x9C000180 | G3.0 | sft cfg 32 | PIN Mux Table Control Register for SPI0S INT & SPI0S CLK |

0x9C000184 | G3.1 | sft cfg 33 | PIN Mux Table Control Register for SPI0S EN & SPI0S DO |

0x9C000188 | G3.2 | sft cfg 34 | PIN Mux Table Control Register for SPI0S DI & SPI1S INT |

0x9C00018C | G3.3 | sft cfg 35 | PIN Mux Table Control Register for SPI1S CLK & SPI1S EN |

0x9C000190 | G3.4 | sft cfg 36 | PIN Mux Table Control Register for SPI1S DO & SPI1S DI |

0x9C000194 | G3.5 | sft cfg 37 | PIN Mux Table Control Register for SPI2S INT & SPI2S CLK |

0x9C000198 | G3.6 | sft cfg 38 | PIN Mux Table Control Register for SPI2S EN & SPI2S DO |

0x9C00019C | G3.7 | sft cfg 39 | PIN Mux Table Control Register for SPI2S DI & SPI3S INT |

0x9C0001A0 | G3.8 | sft cfg 40 | PIN Mux Table Control Register for SPI3S CLK & SPI3S EN |

0x9C0001A4 | G3.9 | sft cfg 41 | PIN Mux Table Control Register for SPI3S DO & SPI3S DI |

0x9C0001A8 | G3.10 | sft cfg 42 | PIN Mux Table Control Register for I2CM0 CK & I2CM0 D |

0x9C0001AC | G3.11 | sft cfg 43 | PIN Mux Table Control Register for I2CM1 CK & I2CM1 D |

0x9C0001B0 | G3.12 | sft cfg 44 | PIN Mux Table Control Register for I2CM2 CK & I2CM2 D |

0x9C0001B4 | G3.13 | sft cfg 45 | PIN Mux Table Control Register for I2CM3 CK & I2CM3 D |

0x9C0001B8 | G3.14 | sft cfg 46 | PIN Mux Table Control Register for UA1 TX & UA1 RX |

0x9C0001BC | G3.15 | sft cfg 47 | PIN Mux Table Control Register for UA1 CTS & UA1 RTS |

0x9C0001C0 | G3.16 | sft cfg 48 | PIN Mux Table Control Register for UA2 TX & UA2 RX |

0x9C0001C4 | G3.17 | sft cfg 49 | PIN Mux Table Control Register for UA2 CTS & UA2 RTS |

0x9C0001C8 | G3.18 | sft cfg 50 | PIN Mux Table Control Register for UA3 TX & UA3 RX |

0x9C0001CC | G3.19 | sft cfg 51 | PIN Mux Table Control Register for UA3 CTS & UA3 RTS |

0x9C0001D0 | G3.20 | sft cfg 52 | PIN Mux Table Control Register for UA4 TX & UA4 RX |

0x9C0001D4 | G3.21 | sft cfg 53 | PIN Mux Table Control Register for UA4 CTS & UA4 RTS |

0x9C0001D8 | G3.22 | sft cfg 54 | PIN Mux Table Control Register for TIMER0 INT & TIMER1 INT |

0x9C0001DC | G3.23 | sft cfg 55 | PIN Mux Table Control Register for TIMER2 INT & TIMER3 INT |

0x9C0001E0 | G3.24 | sft cfg 56 | PIN Mux Table Control Register for GPIO INT0 & GPIO INT1 |

0x9C0001E4 | G3.25 | sft cfg 57 | PIN Mux Table Control Register for GPIO INT2 & GPIO INT3 |

0x9C0001E8 | G3.26 | sft cfg 58 | PIN Mux Table Control Register for GPIO INT4 & GPIO INT5 |

0x9C0001EC | G3.27 | sft cfg 59 | PIN Mux Table Control Register for GPIO INT6 & GPIO INT7 |

0x9C0001F0 | G3.28 | rsv | Reserved |

0x9C0001F4 | G3.29 | rsv | Reserved |

0x9C0001F8 | G3.30 | rsv | Reserved |

0x9C0001FC | G3.31 | rsv | Reserved |

Address | Group No. | Register Name | Register Description |

0x9C000200 | G4.0 | mo4 pllsp ctl 0 | SPDIF PLL Control Register #0 |

0x9C000204 | G4.1 | mo4 pllsp ctl 1 | SPDIF PLL Control Register #1 |

0x9C000208 | G4.2 | mo4 pllsp ctl 2 | SPDIF PLL Control Register #2 |

0x9C00020C | G4.3 | mo4 pllsp ctl 3 | SPDIF PLL Control Register #3 |

0x9C000210 | G4.4 | mo4 pllsp ctl 4 | SPDIF PLL Control Register #4 |

0x9C000214 | G4.5 | mo4 pllsp ctl 5 | SPDIF PLL Control Register #5 |

0x9C000218 | G4.6 | mo4 pllsp ctl 6 | SPDIF PLL Control Register #6 |

0x9C00021C | G4.7 | mo4 plla ctl 0 | PLLA Control Register #0 |

0x9C000220 | G4.8 | mo4 plla ctl 1 | PLLA Control Register #1 |

0x9C000224 | G4.9 | mo4 plla ctl 2 | PLLA Control Register #2 |

0x9C000228 | G4.10 | mo4 plla ctl 3 | PLLA Control Register #3 |

0x9C00022C | G4.11 | mo4 plla ctl 4 | PLLA Control Register #4 |

0x9C000230 | G4.12 | mo4 plle ctl | PLLE Control Register #0 |

0x9C000234 | G4.13 | mo4 pllf ctl | PLLF Control Register #0 |

0x9C000238 | G4.14 | mo4 plltv ctl 0 | PLLTV Control Register #0 |

0x9C00023C | G4.15 | mo4 plltv ctl 1 | PLLTV Control Register #1 |

0x9C000240 | G4.16 | mo4 plltv ctl 2 | PLLTV Control Register #2 |

0x9C000244 | G4.17 | mo4 usbc ctl | USBC Control Register |

0x9C000248 | G4.18 | mo4 uphy0 ctl0 | UPHY0 Control Register#0 |

0x9C00024C | G4.19 | mo4 uphy0 ctl1 | UPHY0 Control Register#1 |

0x9C000250 | G4.20 | mo4 uphy0 ctl2 | UPHY0 Control Register#2 |

0x9C000254 | G4.21 | mo4 uphy0 ctl3 | UPHY0 Control Register#3 |

0x9C000258 | G4.22 | mo4 uphy1 ctl0 | UPHY1 Control Register#0 |

0x9C00025C | G4.23 | mo4 uphy1 ctl1 | UPHY1 Control Register#1 |

0x9C000260 | G4.24 | mo4 uphy1 ctl2 | UPHY1 Control Register#2 |

0x9C000264 | G4.25 | mo4 uphy1 ctl3 | UPHY1 Control Register#3 |

0x9C000268 | G4.26 | mo4 pllsys | PLLSYS |

0x9C00026C | G4.27 | mo clk sel0 | Clock Setting and Selection Register |

0x9C000270 | G4.28 | MO PROBE SEL | Probe module selection |

0x9C000274 | G4.29 | mo4 misc ctl 0 | Miscellaneous Control Register #0 |

0x9C000278 | G4.30 | mo4 uphy0 sts | Reserved |

0x9C00027C | G4.31 | Reserved | Reserved |

Address | Group No. | Register Name | Register Description |

0x9C000280 | G5.0 | mo5 thermal ctl 0 | Thermal Control register #0 |

0x9C000284 | G5.1 | mo5 thermal ctl 1 | Thermal Control register #1 |

0x9C000288 | G5.2 | mo5 thermal ctl 2 | Thermal Control register #2 |

0x9C00028C | G5.3 | mo5 thermal ctl 3 | Thermal Control register #3 |

0x9C000290 | G5.4 | mo5 tmds l2sw ctl | TMDS L2SW Control Register |

0x9C000294 | G5.5 | mo5 l2sw clksw ctl | L2SW Clock Switch Control Register |

0x9C000298 | G5.6 | mo5 I2C2BUS ctl | I2C2BUS Control Register |

0x9C00029C | G5.7 | pfcnt ctl | PFCNT Register |

0x9C0002A0 | G5.8 | pfcnt sensor ctl 0 | PFCNT SENSOR Register #0 |

0x9C0002A4 | G5.9 | pfcnt sensor ctl 1 | PFCNT SENSOR Register #1 |

0x9C0002A8 | G5.10 | pfctn sts 0 | PFCNT Macro Status Register |

0x9C0002AC | G5.11 | pfctn sts 1 | PFCNT SENSOR Staus Register |

0x9C0002B0 | G5.12 | thermal sts 0 | THERMAL Status Register #0 |

0x9C0002B4 | G5.13 | thermal sts 1 | Reserved |

0x9C0002B8 | G5.14 | rsv | Reserved |

0x9C0002BC | G5.15 | rsv | Reserved |

0x9C0002C0 | G5.16 | rsv | Reserved |

0x9C0002C4 | G5.17 | rsv | Reserved |

0x9C0002C8 | G5.18 | rsv | Reserved |

0x9C0002CC | G5.19 | rsv | Reserved |

0x9C0002D0 | G5.20 | rsv | Reserved |

0x9C0002D4 | G5.21 | rsv | Reserved |

0x9C0002D8 | G5.22 | rsv | Reserved |

0x9C0002DC | G5.23 | DC09 CTL 0 | DC 0.9V Control Register #0 |

0x9C0002E0 | G5.24 | DC09 CTL 1 | DC 0.9V Control Register #1 |

0x9C0002E4 | G5.25 | DC09 CTL 2 | DC 0.9V Control Register #2 |

0x9C0002E8 | G5.26 | DC12 CTL 0 | DC 1.2V Control Register #0 |

0x9C0002EC | G5.27 | DC12 CTL 1 | DC 1.2V Control Register #1 |

0x9C0002F0 | G5.28 | DC12 CTL 2 | DC 1.2V Control Register #2 |

0x9C0002F4 | G5.29 | DC15 CTL 0 | DC 1.5V Control Register #0 |

0x9C0002F8 | G5.30 | DC15 CTL 1 | DC 1.5V Control Register #1 |

0x9C0002FC | G5.31 | DC15 CTL 2 | DC 1.5V Control Register #2 |

Address | Group No. | Register Name | Register Description |

0x9C000300 | G6.0 | gpio ctl sel 0 | GPIO Control Source Selection Register #0 |

0x9C000304 | G6.1 | gpio ctl sel 1 | GPIO Control Source Selection Register #1 |

0x9C000308 | G6.2 | gpio ctl sel 2 | GPIO Control Source Selection Register #2 |

0x9C00030C | G6.3 | gpio ctl sel 3 | GPIO Control Source Selection Register #3 |

0x9C000310 | G6.4 | gpio ctl sel 4 | GPIO Control Source Selection Register #4 |

0x9C000314 | G6.5 | gpio ctl sel 5 | GPIO Control Source Selection Register #5 |

0x9C000318 | G6.6 | gpio ctl sel 6 | GPIO Control Source Selection Register #6 |

0x9C00031C | G6.7 | gpio ctl sel 7 | GPIO Control Source Selection Register #7 |

0x9C000320 | G6.8 | gpio oe 0 | GPIO Output Enable Register #0 |

0x9C000324 | G6.9 | gpio oe 1 | GPIO Output Enable Register #1 |

0x9C000328 | G6.10 | gpio oe 2 | GPIO Output Enable Register #2 |

0x9C00032C | G6.11 | gpio oe 3 | GPIO Output Enable Register #3 |

0x9C000330 | G6.12 | gpio oe 4 | GPIO Output Enable Register #4 |

0x9C000334 | G6.13 | gpio oe 5 | GPIO Output Enable Register #5 |

0x9C000338 | G6.14 | gpio oe 6 | GPIO Output Enable Register #6 |

0x9C00033C | G6.15 | gpio oe 7 | GPIO Output Enable Register #7 |

0x9C000340 | G6.16 | gpio o 0 | GPIO Output Data Register #0 |

0x9C000344 | G6.17 | gpio o 1 | GPIO Output Data Register #1 |

0x9C000348 | G6.18 | gpio o 2 | GPIO Output Data Register #2 |

0x9C00034C | G6.19 | gpio o 3 | GPIO Output Data Register #3 |

0x9C000350 | G6.20 | gpio o 4 | GPIO Output Data Register #4 |

0x9C000354 | G6.21 | gpio o 5 | GPIO Output Data Register #5 |

0x9C000358 | G6.22 | gpio o 6 | GPIO Output Data Register #6 |

0x9C00035C | G6.23 | gpio o 7 | GPIO Output Data Register #7 |

0x9C000360 | G6.24 | gpio in 0 | GPIO Input Data Register #0 |

0x9C000364 | G6.25 | gpio in 1 | GPIO Input Data Register #1 |

0x9C000368 | G6.26 | gpio in 2 | GPIO Input Data Register #2 |

0x9C00036C | G6.27 | gpio in 3 | GPIO Input Data Register #3 |

0x9C000370 | G6.28 | gpio in 4 | GPIO Input Data Register #4 |

0x9C000374 | G6.29 | gpio in 5 | GPIO Input Data Register #5 |

0x9C000378 | G6.30 | rsv | Reserved |

0x9C00037C | G6.31 | rsv | Reserved |

Address | Group No. | Register Name | Register Description |

0x9C000380 | G7.0 | gpio in inv 0 | GPIO Input Invert Register #0 |

0x9C000384 | G7.1 | gpio in inv 1 | GPIO Input Invert Register #1 |

0x9C000388 | G7.2 | gpio in inv 2 | GPIO Input Invert Register #2 |

0x9C00038C | G7.3 | gpio in inv 3 | GPIO Input Invert Register #3 |

0x9C000390 | G7.4 | gpio in inv 4 | GPIO Input Invert Register #4 |

0x9C000394 | G7.5 | gpio in inv 5 | GPIO Input Invert Register #5 |

0x9C000398 | G7.6 | gpio in inv 6 | GPIO Input Invert Register #6 |

0x9C00039C | G7.7 | gpio in inv 7 | GPIO Input Invert Register #7 |

0x9C0003A0 | G7.8 | gpio out inv 0 | GPIO Output Invert Register #0 |

0x9C0003A4 | G7.9 | gpio out inv 1 | GPIO Output Invert Register #1 |

0x9C0003A8 | G7.10 | gpio out inv 2 | GPIO Output Invert Register #2 |

0x9C0003AC | G7.11 | gpio out inv 3 | GPIO Output Invert Register #3 |

0x9C0003B0 | G7.12 | gpio out inv 4 | GPIO Output Invert Register #4 |

0x9C0003B4 | G7.13 | gpio out inv 5 | GPIO Output Invert Register #5 |

0x9C0003B8 | G7.14 | gpio out inv 6 | GPIO Output Invert Register #6 |

0x9C0003BC | G7.15 | gpio out inv 7 | GPIO Output Invert Register #7 |

0x9C0003C0 | G7.16 | gpio od 0 | GPIO OD Register #0 |

0x9C0003C4 | G7.17 | gpio od 1 | GPIO OD Register #1 |

0x9C0003C8 | G7.18 | gpio od 2 | GPIO OD Register #2 |

0x9C0003CC | G7.19 | gpio od 3 | GPIO OD Register #3 |

0x9C0003D0 | G7.20 | gpio od 4 | GPIO OD Register #4 |

0x9C0003D4 | G7.21 | gpio od 5 | GPIO OD Register #5 |

0x9C0003D8 | G7.22 | gpio od 6 | GPIO OD Register #6 |

0x9C0003DC | G7.23 | gpio od 7 | GPIO OD Register #7 |

0x9C0003E0 | G7.24 | rsv | Reserved |

0x9C0003E4 | G7.25 | rsv | Reserved |

0x9C0003E8 | G7.26 | rsv | Reserved |

0x9C0003EC | G7.27 | rsv | Reserved |

0x9C0003F0 | G7.28 | rsv | Reserved |

0x9C0003F4 | G7.29 | rsv | Reserved |

0x9C0003F8 | G7.30 | rsv | Reserved |

0x9C0003FC | G7.31 | rsv | Reserved |

7.10.2 Registers Description

RGST Table Group 0 MOON

0.0 Chip Revision Stamp ID Register (mo stamp)

Address: 0x9C000000

Reset: 0x0000 0B10

| Field Name | Bit | Access | Description |

| MO STAMP | 31:0 | RO | Chip Revision Stamp ID |

0.1 Clock Enable Register #0 (mo clken0)

Address: 0x9C000004

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| PERI1 CLKEN | 15 | RW | PERI1 Hardware Clock Enable 0: Disable 1: Enable (default) |

| UMCTL2 CLKEN | 14 | RW | SDCTRL0 Hardware Clock Enable 0: Disable 1: Enable (default) |

A926 CLKEN | 13 | RW | A926 Hardware Clock Enable |

Reserved | 12 | RW | RESERVED |

PERI0 CLKEN | 11 | RW | PERI0 Hardware Clock Enable |

SDCTRL0 CLKEN | 10 | RW | SDCTRL Hardware Clock Enable |

SPIFL CLKEN | 9 | RW | SPIFL Hardware Clock Enable |

RBUS L00 CLKEN | 8 | RW | RBUS L00 Hardware Clock Enable |

BR CLKEN | 7 | RW | BR Hardware Clock Enable |

NOC CLKEN | 6 | RW | NOC Hardware Clock Enable |

Reserved | 5 | RW | RESERVED |

IOP CLKEN | 4 | RW | IOP Hardware Clock Enable |

IOCTL CLKEN | 3 | IO CTL Hardware Clock Enable | |

RTC CLKEN | 2 | RW | RTC Hardware Clock Enable |

Reserved | 1 | RESERVED | |

SYSTEM CLKEN | 0 | RW | SYSTEM Hardware Clock Enable |

0.2 Clock Enable Register #1 (mo clken1)

Address: 0x9C000008

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| UADMA CLKEN | 15 | RW | UADMA Hardware Clock Enable 0: Disable 1: Enable (default) |

| DDC0 CLKEN | 14 | RW | DDC0 Hardware Clock Enable 0: Disable 1: Enable (default) |

| HWUA | 13 | RW | HWUA Hardware Clock Enable 0: Disable 1: Enable (default) |

| UA4 CLKEN | 12 | RW | UA4 Hardware Clock Enable 0: Disable 1: Enable (default) |

| UA3 CLKEN | 11 | RW | UA3 Hardware Clock Enable 0: Disable 1: Enable (default) |

| UA2 CLKEN | 10 | RW | UA2 Hardware Clock Enable 0: Disable 1: Enable (default) |

| UA1 CLKEN | 9 | RW | UA1 Hardware Clock Enable 0: Disable 1: Enable (default) |

| UA0 CLKEN | 8 | RW | UA0 Hardware Clock Enable 0: Disable 1: Enable (default) |

| STC AV2 CLKEN | 7 | RW | STC AV2 Hardware Clock Enable 0: Disable 1: Enable (default) |

| STC AV1 CLKEN | 6 | RW | STC AV1 Hardware Clock Enable 0: Disable 1: Enable (default) |

STC AV0 CLKEN | 5 | RW | STC AV0 Hardware Clock Enable |

STC0 CLKEN | 4 | RW | STC0 Hardware Clock Enable |

Reserved | 3 | RW | RESERVED |

CHIP CLKEN | 2 | RW | TRACER Hardware Clock Enable |

Reserved | 1 | RW | RESERVED |

DDR PHY0 CLKEN | 0 | RW | DDR PHY0 Hardware Clock Enable |

0.3 Clock Enable Register #2 (mo clken2)

Address: 0x9C00000C

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15 | RW | RESERVED |

| UPHY1 CLKEN | 14 | RW | UPHY1 Hardware Clock Enable 0: Disable 1: Enable (default) |

| UPHY0 CLKEN | 13 | RW | UPHY0 Hardware Clock Enable 0: Disable 1: Enable (default) |

| Reserved | 12 | RW | RESERVED |

| USBC1 CLKEN | 11 | RW | USBC1 Hardware Clock Enable 0: Disable 1: Enable (default) |

USBC0 CLKEN | 10 | RW | USBC0 Hardware Clock Enable |

Reserved | 9:7 | RW | RESERVED |

AUD CLKEN | 6 | RW | AUD Hardware Clock Enable |

SPI COMBO 3 CLKEN | 5 | RW | SPI COMBO 3 Hardware Clock Enable |

SPI COMBO 2 CLKEN | 4 | RW | SPI COMBO 2 Hardware Clock Enable |

SPI COMBO 1 CLKEN | 3 | RW | SPI COMBO 1 Hardware Clock Enable |

SPI COMBO 0 CLKEN | 2 | RW | SPI COMBO 0 Hardware Clock Enable |

CBDMA1 CLKEN | 1 | RW | CBDMA1 Hardware Clock Enable |

CBDMA0 CLKEN | 0 | RW | CBDMA0 Hardware Clock Enable |

0.4 Clock Enable Register #3 (mo clken3)

Address: 0x9C000010

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| CARD CTL1 CLKEN | 15 | RW | CARD CTL1 Hardware Clock Enable 0: Disable 1: Enable (default) |

CARD CTL0 CLKEN | 14 | RW | CARD CTL0 Hardware Clock Enable |

PMC CLKEN | 13 | RW | PMC Hardware Clock Enable |

Reserved | 12:4 | RW | RESERVED |

I2CM3 CLKEN | 3 | RW | I2CM3 Hardware Clock Enable |

I2CM2 CLKEN | 2 | RW | I2CM2 Hardware Clock Enable |

I2CM1 CLKEN | 1 | RW | I2CM1 Hardware Clock Enable |

I2CM0 CLKEN | 0 | RW | I2CM0 Hardware Clock Enable |

0.5 Clock Enable Register #4 (mo clken4)

Address: 0x9C000014

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| MIPICSI1 CLKEN | 15 | RW | MIPI CSI1 Hardware Clock Enable 0: Disable 1: Enable (default) |

| MIPICSI0 CLKEN | 14 | RW | MIPI CSI0 Hardware Clock Enable 0: Disable 1: Enable (default) |

| CSIIW1 CLKEN | 13 | RW | CSIIW1 Hardware Clock Enable 0: Disable 1: Enable (default) |

CSIIW0 CLKEN | 12 | RW | CSIIW0 Hardware Clock Enable |

DDFCH CLKEN | 11 | RW | DDFCH Hardware Clock Enable |

Reserved | 10:5 | RW | RESERVED |

BCH CLKEN | 4 | RW | BCH Hardware Clock Enable |

Reserved | 3 | RW | RESERVED |

CARD CTL4 CLKEN | 2 | RW | CARD CTL4 Hardware Clock Enable |

Reserved | 1:0 | RW | RESERVED |

0.6 Clock Enable Register #5 (mo clken5)

Address: 0x9C000018

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:6 | RW | RESERVED |

| VPOST CLKEN | 5 | RW | VPOST Hardware Clock Enable 0: Disable 1: Enable (default) |

| Reserved | 4:1 | RW | RESERVED |

| HDMI TX CLKEN | 0 | RW | HDMI TX Hardware Clock Enable 0: Disable 1: Enable (default) |

0.7 Clock Enable Register #6 (mo clken6)

Address: 0x9C00001C

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| INTERRUPT CLKEN | 15 | RW | INTERRUPT Hardware Clock Enable 0: Disable 1: Enable (default) |

| Reserved | 14:11 | RW | RESERVED |

| TCON CLKEN | 10 | RW | TCON Hardware Clock Enable 0: Disable 1: Enable (default) |

| Reserved | 9:2 | RW | RESERVED |

| DMIX CLKEN | 1 | RW | DMIX Hardware Clock Enable 0: Disable 1: Enable (default) |

| TGEN CLKEN | 0 | RW | TGEN Hardware Clock Enable 0: Disable 1: Enable (default) |

0.8 Clock Enable Register #7 (mo clken7)

Address: 0x9C000020

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:5 | RW | RESERVED |

| RBUS TOP CLKEN | 4 | RW | RBUS TOP Hardware Clock Enable 0: Disable 1: Enable (default) |

| GPIO CLKEN | 3 | RW | GPIO Hardware Clock Enable 0: Disable 1: Enable (default) |

| Reserved | 2:1 | RW | RESERVED |

| RGST CLKEN | 0 | RW | RGST Hardware Clock Enable 0: Disable 1: Enable (default) |

0.9 Clock Enable Register #8 (mo clken8)

Address: 0x9C000024

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:12 | RW | RESERVED |

| I2C2CBUS CLKEN | 11 | RW | I2C2CBUS Hardware Clock Enable 0: Disable (default) 1: Enable |

| SPIND CLKEN | 10 | RW | SPI NAND Hardware Clock Enable 0: Disable (default) 1: Enable |

| Reserved | 9:7 | RW | RESERVED |

| MAILBOX CLKEN | 6 | RW | MAILBOX Hardware Clock Enable 0: Disable 1: Enable (default) |

| Reserved | 5:0 | RW | RESERVED |

0.10 Clock Enable Register #9 (mo clken9)

Address: 0x9C000028

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

Reserved | 15:10 | RO | RESERVED |

AXI GLOBAL CLKEN | 9 | RW | AXI GLOBAL Hardware IP Clock Enable |

ICM CLKEN | 8 | RW | ICM Hardware IP Clock Enable |

L2SW CLKEN | 7 | RW | L2SW Hardware IP Clock Enable |

FPGA CLKEN | 6 | RW | FPGA Hardware IP Clock Enable |

FIO CTL CLKEN | 5 | RW | FIO CTL Hardware IP Clock Enable |

DUMMY MASTER CLKEN | 4 | RW | DUMMY MASTER Hardware IP Clock Enable |

UADBG CLKEN | 3 | RW | UADBG Hardware IP Clock Enable |

DISP PWM CLKEN | 2 | RW | DISP PWM Hardware IP Clock Enable |

| Reserved | 1 | RW | RESERVED |

OSD0 CLKEN | 0 | RW | OSD0 Hardware IP Clock Enable |

0.11 Clock Gating Enable Register #0 (mo gclken0)

Address: 0x9C00002C

Reset: 0x0000 FFBF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

PERI1 GCLKEN | 15 | RW | PERI1 Hardware Clock-Gating Enable |

UMCTL2 GCLKEN | 14 | RW | SDCTRL0 Hardware Clock-Gating Enable |

A926 GCLKEN | 13 | RW | A926 Hardware Clock-Gating Enable |

Reserved | 12 | RW | RESERVED |

PERI0 GCLKEN | 11 | RW | PERI0 Hardware Clock-Gating Enable |

SDCTRL0 GCLKEN | 10 | RW | SDCTRL Hardware Clock-Gating Enable |

SPIFL GCLKEN | 9 | RW | SPIFL Hardware Clock-Gating Enable |

RBUS L00 GCLKEN | 8 | RW | RBUS L00 Hardware Clock-Gating Enable |

BR GCLKEN | 7 | RW | BR Hardware Clock-Gating Enable |

NOC GCLKEN | 6 | RW | NOC Hardware Clock-Gating Enable |

Reserved | 5 | RW | Reserved |

IOP GCLKEN | 4 | RW | IOP Hardware Clock-Gating Enable |

IOCTL GCLKEN | 3 | RW | IO CTL Hardware Clock-Gating Enable |

RTC GCLKEN | 2 | RW | RTC Hardware Clock-Gating Enable |

| Reserved | 1 | RW | reserved |

| SYSTEM GCLKEN | 0 | RW | SYSTEM Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

0.12 Clock Gating Enable Register #1 (mo gclken1)

Address: 0x9C000030

Reset: 0x0000 FFFD

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| UADMA GCLKEN | 15 | RW | UADMA Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| DDC0 GCLKEN | 14 | RW | DDC0 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| HWUA | 13 | RW | HWUA Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| UA4 GCLKEN | 12 | RW | UA4 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| UA3 GCLKEN | 11 | RW | UA3 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| UA2 GCLKEN | 10 | RW | UA2 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| UA1 GCLKEN | 9 | RW | UA1 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

UA0 GCLKEN | 8 | RW | UA0 Hardware Clock-Gating Enable |

STC AV2 GCLKEN | 7 | RW | STC AV2 Hardware Clock-Gating Enable |

STC AV1 GCLKEN | 6 | RW | STC AV1 Hardware Clock-Gating Enable |

STC AV0 GCLKEN | 5 | RW | STC AV0 Hardware Clock-Gating Enable |

STC0 GCLKEN | 4 | RW | STC0 Hardware Clock-Gating Enable |

Reserved | 3 | RW | RESERVED |

CHIP GCLKEN | 2 | RW | TRACER Hardware Clock-Gating Enable |

Reserved | 1 | RW | RESERVED |

DDR PHY0 GCLKEN | 0 | RW | DDR PHY0 Hardware Clock-Gating Enable |

0.13 Clock Gating Enable Register #2 (mo gclken2)

Address: 0x9C000034

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15 | RW | RESERVED |

| UPHY1 GCLKEN | 14 | RW | UPHY1 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

UPHY0 GCLKEN | 13 | RW | UPHY0 Hardware Clock-Gating Enable |

Reserved | 12 | RW | RESERVED |

USBC1 GCLKEN | 11 | RW | USBC1 Hardware Clock-Gating Enable |

USBC0 GCLKEN | 10 | RW | USBC0 Hardware Clock-Gating Enable |

Reserved | 9:7 | RW | RESERVED |

AUD GCLKEN | 6 | RW | AUD Hardware Clock-Gating Enable |

SPI COMBO 3 GCLKEN | 5 | RW | SPI COMBO 3 Hardware Clock-Gating Enable |

SPI COMBO 2 GCLKEN | 4 | RW | SPI COMBO 2 Hardware Clock-Gating Enable |

SPI COMBO 1 GCLKEN | 3 | RW | SPI COMBO 1 Hardware Clock-Gating Enable |

SPI COMBO 0 GCLKEN | 2 | RW | SPI COMBO 0 Hardware Clock-Gating Enable |

CBDMA1 GCLKEN | 1 | RW | CBDMA1 Hardware Clock-Gating Enable |

CBDMA0 GCLKEN | 0 | RW | CBDMA0 Hardware Clock-Gating Enable |

0.14 Clock Gating Enable Register #3 (mo gclken3)

Address: 0x9C000038

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| CARD CTL1 GCLKEN | 15 | RW | CARD CTL1 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| CARD CTL0 GCLKEN | 14 | RW | CARD CTL0 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| PMC GCLKEN | 13 | RW | PMC Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| Reserved | 12:4 | RW | RESERVED |

| I2CM3 GCLKEN | 3 | RW | I2CM3 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| I2CM2 GCLKEN | 2 | RW | I2CM2 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| I2CM1 GCLKEN | 1 | RW | I2CM1 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| I2CM0 GCLKEN | 0 | RW | I2CM0 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

0.15 Clock Gating Enable Register #4 (mo gclken4)

Address: 0x9C00003C

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| MIPICSI1 GCLKEN | 15 | RW | MIPI CSI1 Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

MIPICSI0 GCLKEN | 14 | RW | MIPI CSI0 Hardware Clock-Gating Enable |

CSIIW1 GCLKEN | 23 | RW | CSIIW1 Hardware Clock-Gating Enable |

CSIIW0 GCLKEN | 12 | RW | CSIIW0 Hardware Clock-Gating Enable |

DDFCH GCLKEN | 11 | RW | DDFCH Hardware Clock-Gating Enable |

Reserved | 10:5 | RW | RESERVED |

BCH GCLKEN | 4 | RW | BCH Hardware Clock-Gating Enable |

Reserved | 3 | RW | RESERVED |

CARD CTL4 GCLKEN | 2 | RW | CARD CTL4 Hardware Clock-Gating Enable |

Reserved | 1:0 | RW | RESERVED |

0.16 Clock Gating Enable Register #5 (mo gclken5)

Address: 0x9C000040

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:6 | RW | RESERVED |

| VPOST GCLKEN | 5 | RW | VPOST Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| Reserved | 4:1 | RW | RESERVED |

| HDMI TX GCLKEN | 0 | RW | HDMI TX Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

0.17 Clock Gating Enable Register #6 (mo gclken6)

Address: 0x9C000044

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| INTERRUPT GCLKEN | 15 | RW | INTERRUPT Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| Reserved | 14:11 | RW | RESERVED |

| TCON GCLKEN | 10 | RW | TCON Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| Reserved | 9:2 | RW | RESERVED |

| DMIX GCLKEN | 1 | RW | DMIX Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| TGEN GCLKEN | 0 | RW | TGEN Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

0.18 Clock Gating Enable Register #7 (mo gclken7)

Address: 0x9C000048

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:5 | RW | RESERVED |

| RBUS TOP GCLKEN | 4 | RW | RBUS TOP Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| GPIO GCLKEN | 3 | RW | GPIO Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| Reserved | 2:1 | RW | RESERVED |

| RGST GCLKEN | 0 | RW | RGST Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

0.19 Clock Gating Enable Register #8 (mo gclken8)

Address: 0x9C00004C

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:12 | RW | RESERVED |

| I2C2CBUS GCLKEN | 11 | RW | I2C2CBUS Hardware Clock-Gating Enable 0: Disable (default) 1: Enable |

| SPIND GCLKEN | 10 | RW | SPI NAND Hardware Clock-Gating Enable 0: Disable (default) 1: Enable |

| Reserved | 9:7 | RW | RESERVED |

| MAILBOX GCLKEN | 6 | RW | MAILBOX Hardware Clock-Gating Enable 0: Disable 1: Enable (default) |

| Reserved | 5:0 | RW | RESERVED |

0.20 Clock Gating Enable Register #9 (mo gclken9)

Address: 0x9C000050

Reset: 0x0000 FFFF

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:9 | RO | RESERVED |

| AXI GLOBAL GCLKEN | 8 | RW | AXI GLOBAL Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| ICM GCLKEN | 7 | RW | ICM Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| L2SW GCLKEN | 6 | RW | L2SW Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| FPGA GCLKEN | 5 | RW | FPGA Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| FIO CTL GCLKEN | 4 | RW | FIO CTL Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| DUMMY MASTER GCLKEN | 3 | RW | DUMMY MASTER Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| UADBG GCLKEN | 2 | RW | UADBG Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| DISP PWM GCLKEN | 1 | RW | DISP PWM Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

| OSD0 GCLKEN | 0 | RW | OSD0 Hardware IP Clock-Gating Enable 0: Disable 1: Enable (default) |

0.21 Hardware Reset Control Register #0 (mo reset0)

Address: 0x9C000054

Reset: 0x0000 015D

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

PERI1 RESET | 15 | RW | TPI Hardware IP Reset Enable 0: Disable |

SDCTRL0 RESET | 14 | RW | SDCTRL0 Hardware IP Reset Enable |

A926 RESET | 13 | RW | A926 Hardware IP Reset Enable |

Reserved | 12 | RW | RESERVED |

PERI0 RESET | 11 | RW | PERI0 Hardware IP Reset Enable |

SPI COMBO RESET | 10 | RW | SPI COMBO Hardware IP Reset Enable |

SPIFL RESET | 9 | RW | SPIFL Hardware IP Reset Enable |

RBUS L00 RESET | 8 | RW | RBUS L00 Hardware IP Reset Enable |

BR RESET | 7 | RW | BR Hardware IP Reset Enable |

NOC RESET | 6 | RW | NOC Hardware IP Reset Enable |

Reserved | 5 | RW | RESERVED |

IOP RESET | 4 | RW | IOP Hardware IP Reset Enable |

IOCTL RESET | 3 | RW | IO CTL Hardware IP Reset Enable |

| RTC RESET | 2 | RW | RTC Hardware IP Reset Enable 0: Disable (default) 1: Enable |

| Reserved | 1 | RW | RESERVED |

| SYSTEM RESET | 0 | RW | SYSTEM Hardware Reset Enable 0: Disable (default) 1: Enable |

0.22 Hardware Reset Control Register #1 (mo reset1)

Address: 0x9C000058

Reset: 0x0000 0004

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| UADMA RESET | 15 | RW | UADMA Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| DDC0 RESET | 14 | RW | DDC0 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 13 | RW | RESERVED |

| UA4 RESET | 12 | RW | UA4 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| UA3 RESET | 11 | RW | UA3 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| UA2 RESET | 10 | RW | UA2 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| UA1 RESET | 9 | RW | UA1 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

UA0 RESET | 8 | RW | UA0 Hardware IP Reset Enable |

STC AV2 RESET | 7 | RW | STC AV2 Hardware IP Reset Enable |

STC AV1 RESET | 6 | RW | STC AV1 Hardware IP Reset Enable |

STC AV0 RESET | 5 | RW | STC AV0 Hardware IP Reset Enable |

STC0 RESET | 4 | RW | STC0 Hardware IP Reset Enable |

Reserved | 3 | RW | RESERVED |

CHIP RESET | 2 | RW | TRACER Hardware IP Reset Enable |

Reserved | 1 | RW | RESERVED |

DDR PHY0 RESET | 0 | RW | DDR PHY0 Hardware IP Reset Enable |

0.23 Hardware Reset Control Register #2 (mo reset2)

Address: 0x9C00005C

Reset: 0x0000 0002

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15 | RW | RESERVED |

| UPHY1 RESET | 14 | RW | UPHY1 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

UPHY0 RESET | 13 | RW | UPHY0 Hardware IP Reset Enable |

Reserved | 12 | RW | RESERVED |

USBC1 RESET | 11 | RW | USBC1 Hardware IP Reset Enable |

USBC0 RESET | 10 | RW | USBC0 Hardware IP Reset Enable |

Reserved | 9:7 | RW | RESERVED |

AUD RESET | 6 | RW | AUD Hardware IP Reset Enable |

SPI COMBO 3 RESET | 5 | RW | SPI COMBO 3 Hardware IP Reset Enable |

SPI COMBO 2 RESET | 4 | RW | SPI COMBO 2 Hardware IP Reset Enable |

SPI COMBO 2 RESET | 3 | RW | SPI COMBO 1 Hardware IP Reset Enable |

SPI COMBO 0 RESET | 2 | RW | SPI COMBO 0 Hardware IP Reset Enable |

CBDMA1 RESET | 1 | RW | CBDMA1 Hardware IP Reset Enable |

CBDMA0 RESET | 0 | RW | CBDMA0 Hardware IP Reset Enable |

0.24 Hardware Reset Control Register #3 (mo reset3)

Address: 0x9C000060

Reset: 0x0000 3000

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| CARD1 CTL1 RESET | 15 | RW | CARD CTL1 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| CARD CTL0 RESET | 14 | RW | CARD CTL0 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| PMC RESET | 13 | RW | PMC Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 12:4 | RW | RESERVED |

| I2CM3 RESET3 | 3 | RW | I2CM3 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| I2CM2 RESET2 | 2 | RW | I2CM2 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| I2CM1 RESET1 | 1 | RW | I2CM1 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| I2CM0 RESET0 | 0 | RW | I2CM0 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

0.25 Hardware Reset Control Register #4 (mo reset4)

Address: 0x9C000064

Reset: 0x0000 0100

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| MIPICSI1 GCLKEN | 15 | RW | MIPI CSI1 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

MIPICSI0 GCLKEN | 14 | RW | MIPI CSI0 Hardware IP Reset Enable |

CSIIW1 GCLKEN | 13 | RW | CSIIW1 Hardware IP Reset Enable |

CSIIW0 GCLKEN | 12 | RW | CSIIW0 Hardware IP Reset Enable |

DDFCH0 GCLKEN | 11 | RW | DDFCH0 Hardware IP Reset Enable |

Reserved | 10:5 | RW | RESERVED |

BCH RESET | 4 | RW | BCH Hardware IP Reset Enable |

Reserved | 3 | RW | RESERVED |

CARD4 CTL1 RESET | 2 | RW | CARD CTL4 Hardware IP Reset Enable |

Reserved | 1:0 | RW | RESERVED |

0.26 Hardware Reset Control Register #5 (mo reset5)

Address: 0x9C000068

Reset: 0x0000 0100

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:6 | RW | RESERVED |

| VPOST GCLKEN | 5 | RW | VPOST Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 4:1 | RW | RESERVED |

| HDMI CTL1 RESET | 0 | RW | HDMI Hardware IP Reset Enable 0: Disable 1: Enable (default) |

0.27 Hardware Reset Control Register #6 (mo reset6)

Address: 0x9C00006C

Reset: 0x0000 0000

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| INTERRUPT RESET | 15 | RW | INTERRUPT Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 14:11 | RW | RESERVED |

| TCON RESET | 10 | RW | TCON Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 9:2 | RW | RESERVED |

| DMIX RESET | 1 | RW | DMIX Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| TGEN RESET | 0 | RW | TGEN Hardware IP Reset Enable 0: Disable 1: Enable (default) |

0.28 Hardware Reset Control Register #7 (mo reset7)

Address: 0x9C000070

Reset: 0x0000 0010

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:5 | RW | RESERVED |

| RBUS TOP RESET | 4 | RW | RBUS TOP Hardware IP Reset Enable 0: Disable (default) 1: Enable |

| GPIO RESET | 3 | RW | GPIO Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 2:1 | RW | RESERVED |

| RGST RESET | 0 | RW | RGST Hardware IP Reset Enable 0: Disable 1: Enable (default) |

0.29 Hardware Reset Control Register #8 (mo reset8)

Address: 0x9C000074

Reset: 0x0000 0300

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| GPOST0 RESET | 15 | RW | GPOST Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| DVE RESET | 14 | RW | DVE Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| SEC RESET | 13 | RW | SEC Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| GDMA RESET | 12 | RW | GDMA Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| I2C2CBUS RESET | 11 | RW | I2C2CBUS Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| SPIND RESET | 10 | RW | SPI NAND Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 9:7 | RW | RESERVED |

| MAILBOX RESET | 6 | RW | MAILBOX Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| Reserved | 5:0 | RW | RESERVED |

0.30 Hardware Reset Control Register #9 (mo reset9)

Address: 0x9C000078

Reset: 0x0000 0080

| Field Name | Bit | Access | Description |

| Mask bit | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:9 | RO | RESERVED |

| AXI GLOBAL RESET | 8 | RW | AXI GLOBAL Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| ICM RESET | 7 | RW | ICM Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| L2SW RESET | 6 | RW | L2SW Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| FPGA RESET | 5 | RW | FPGA Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| FIO CTL RESET | 4 | RW | FIO CTL Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| DUMMY MASTER RESET | 3 | RW | DUMMY MASTER Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| UADBG RESET | 2 | RW | UADBG Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| DISP PWM RESET | 1 | RW | DISP PWM Hardware IP Reset Enable 0: Disable 1: Enable (default) |

| OSD0 RESET | 0 | RW | OSD0 Hardware IP Reset Enable 0: Disable 1: Enable (default) |

0.31 Software Configure Hardware Mode (mo sft cfg mode)

Address: 0x9C00007C

Reset: 0x0

| Field Name | Bit | Access | Description |

| Reserved | 31:5 | RO | RESERVED |

| Reserved | 16:10 | RO | RESERVED |

| Reserved | 9:5 | RO | RESERVED |

| Reserved | 4:0 | RU | RESERVED |

RGST Table Group 1 MOON 1

1.0 Test Mode Control Register (sft cfg 0)

Address:0x9C000080

Reset:0x0

| Field Name | Bit | Access | Description |

| reserved | 31:8 | RW | RESERVED |

| reserved | 17 | RW | RESERVED |

| SFT CFG RTC TEST SEL | 16 | RW | RTC TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG USB1 TEST SEL | 15 | RW | USB1 TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG USB0 TEST SEL | 14 | RW | USB0 TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PLLSPDIF TEST SEL | 13 | RW | PLLSPDIF TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PLLTV TEST SEL | 12 | RW | PLLTV TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PLLE TEST SEL | 11 | RW | PLLE TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PLLF TEST SEL | 10 | RW | PLLF TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PLLSYS C TEST SEL | 9 | RW | PLLSYS C TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PLLA TEST SEL | 8 | RW | PLLA TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG DDRIO TEST SEL | 7 | RW | DDRIO TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG DDR SSCPLL TEST SEL | 6 | RW | DDR SSCPLL TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

Reserved | 5 | RW | RESERVED |

| SFT CFG THERMAL TEST SEL | 4 | RW | THERMAL TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG TMDSTX TEST SEL | 3 | RW | TMDSTX TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG MIPIDPHY1 TEST SEL | 2 | RW | MIPIDPHY1 TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG MIPIDPHY0 TEST SEL | 1 | RW | MIPIDPHY0 TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG CHIP PINMUX TEST SEL | 0 | RW | CHIP PINMUX TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

1.1 PIN Mux Table Control Register #1 (sft cfg 1)

Address: 0x9C000084

Reset:0x0

| Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| SFT CFG AUD EXT ADC IFX0 SEL | 15 | RW | AUD EXT ADC IFX0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG HDMI TX SEL | 14:13 | HDMI TX Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion | |

| SFT CFG FPGA IFX SEL | 12 | RW | FPGA IFX Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG CHIP UA2AXI SEL | 11:10 | RW | CHIP UA2AXI Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

| SFT CFG CHIP DEBUG SEL | 9:8 | RW | CHIP DEBUG Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

| SFT CFG UA0 SEL | 7 | RW | UA0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG SD CARD SEL | 6 | RW | SD CARD Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG CARD0 EMMC SEL | 5 | RW | CARD0 EMMC Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG SPI NAND SEL | 4 | RW | SPI NAND Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG SPI FLASH 4BIT SEL | 3:2 | RW | SPI FLASH 4BIT Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

| SFT CFG SPI FLASH SEL | 1:0 | RW | SPI FLASH Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

1.2 PIN Mux Table Control Register #2 (sft cfg 2)

Address: 0x9C000088

Reset: 0x0

| Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

SFT CFG UPHY0 IF SEL | 15:14 | RW | UPHY0 IF Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

SFT CFG UADBG SEL | 13:12 | RW | UADBG Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

SFT CFG IR IN SEL | 11 | RW | IR IN Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG SLV I2C SEL | 10 | RW | SLV I2C Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG DBG I2C SEL | 9 | RW | DBG I2C Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG CLKGENA SEL | 8 | RW | CLKGENA Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG PCM IEC TX SEL | 7 | RW | PCM IEC TX Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG PDMRX IFX0 SEL | 6 | RW | PDMRX IFX0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG TDMRX IFX0 SEL | 5 | RW | TDMRX IFX0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG TDMTX IFX0 SEL | 4 | RW | TDMTX IFX0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG IEC TX SEL | 3 | RW | IEC TX Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG AUD IEC RX0 SEL | 2 | RW | AUD IEC RX0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

SFT CFG AUD TEST SEL | 1 | RW | AUD TEST Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG AUD EXT DAC IFX0 SEL | 0 | RW | AUD EXT DAC IFX0 Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

1.3 PIN Mux Table Control Register #3 (sft cfg 3)

Address: 0x9C00008C

Reset: 0x0

| Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| SFT CFG 8051 JTAG SEL | 15:14 | RW | 8051 JTAG Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

| SFT CFG HWCFG PROB SEL | 13 | RW | HWCFG PROB Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG CLK27 OUT SEL | 12 | RW | CLK27 OUT Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG XCK OUT SEL | 11 | RW | XCK OUT Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG MO1 PLLA 135 147 O SEL | 10 | RW | MO1 PLLA 135 147 O Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG MO1 CLK27 O SEL | 9 | RW | MO1 CLK27 O Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG PROBE PORT SEL | 8:7 | RW | PROBE PORT Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

| SFT CFG UPHY0 EXT SEL | 6 | RW | UPHY0 EXT Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG UPHY1 DEBUG SEL | 5 | RW | UPHY1 DEBUG Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG UPHY0 DEBUG SEL | 4 | RW | UPHY0 DEBUG Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG USBC1 OTG EN SEL | 3 | RW | USBC1 OTG EN Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG USBC0 OTG EN SEL | 2 | RW | USBC0 OTG EN Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| SFT CFG UPHY1 IF SEL | 1:0 | RW | UPHY1 IF Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

1.4 PIN Mux Table Control Register #4 (sft cfg 4)

Address: 0x9C000090

Reset:0x0

| Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| Reserved | 15:7 | RW | RESERVED |

| SFT CFG LCDIF SEL | 6 | RW | LCD Interface Pin-Mux Column Selection Set 1 to select pin mux to this group of funcion |

| Reserved | 5:2 | RW | RESERVED |

| SFT CFG ARM926 JTAG SEL | 1:0 | RW | ARM926 JTAG Pin-Mux Column Selection Set 0~3 to select pin mux to this group of funcion |

1.5 Reserved (rsv)

Address: 0x9C000094

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.6 Reserved (rsv)

Address: 0x9C000098

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.7 Reserved (rsv)

Address: 0x9C00009C

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.7 Reserved (rsv)

Address: 0x9C00009C

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.8 Reserved (rsv)

Address: 0x9C0000A0

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.9 Reserved (rsv)

Address: 0x9C0000A4

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.10 Reserved (rsv)

Address: 0x9C0000A8

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.11 Reserved (rsv)

Address: 0x9C0000AC

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.12 Reserved (rsv)

Address: 0x9C0000B0

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.13 Reserved (rsv)

Address: 0x9C0000B4

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.14 Reserved (rsv)

Address: 0x9C0000B8

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.15 Reserved (rsv)

Address: 0x9C0000BC

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.16 Reserved (rsv)

Address: 0x9C0000C0

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.17 Reserved (rsv)

Address: 0x9C0000C4

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.18 Reserved (rsv)

Address: 0x9C0000C8

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.19 Reserved (rsv)

Address: 0x9C0000CC

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.20 Reserved (rsv)

Address: 0x9C0000D0

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.21 Reserved (rsv)

Address: 0x9C0000D4

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.22 Reserved (rsv)

Address: 0x9C0000D8

Reset:0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.23 Reserved (rsv)

Address: 0x9C0000DC

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.24 Reserved (rsv)

Address: 0x9C0000E0

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.25 Reserved (rsv)

Address: 0x9C0000E4

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.26 Reserved (rsv)

Address: 0x9C0000E8

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.27 Reserved (rsv)

Address: 0x9C0000EC

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.28 Reserved (rsv)

Address: 0x9C0000F0

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.29 Reserved (rsv)

Address: 0x9C0000F4

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.30 Reserved (rsv)

Address: 0x9C0000F8

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

1.31 Reserved (rsv)

Address: 0x9C0000FC

Reset: 0x0

Field Name | Bit | Access | Description |

Reserved | 31:0 | RW | RESERVED |

RGST Table Group 2 MOON 2

2.0 PIN Mux Table Control Register for L2SW CLK & L2SW LED (sft cfg 0)

Address: 0x9C000100

Reset: 0x0

Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| reserved | 15 | RW | RESERVED |

| SFT CFG L2SW LED FLASH0 SEL | 14:8 | RW | L2SW LED FLASH0 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW CLK OUT SEL | 6:0 | RW | L2SW CLK OUT Pin-Mux Column Selection |

2.1 PIN Mux Table Control Register for L2SW LED & L2SW LED (sft cfg 1)

Address: 0x9C000104

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

SFT CFG L2SW LED ON0 SEL | 14:8 | RW | Layer 2 Switch LED ON0 Pin-Mux Column Selection |

reserved | 7 | RW | RESERVED |

| SFT CFG L2SW LED FLASH1 SEL | 6:0 | RW | Layer 2 Switch LED FLASH1 Pin-Mux Column Selection |

2.2 PIN Mux Table Control Register for L2SW LED & L2SW MAC (sft cfg 2)

Address: 0x9C000108

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW MAC SMI MDIO SEL | 14:8 | RW | Layer 2 Switch MAC SMI MDIO Pin-Mux Column Selection |

reserved | 7 | RW | RESERVED |

SFT CFG L2SW LED ON1 SEL | 6:0 | RW | Layer 2 Switch LED ON1 Pin-Mux Column Selection |

2.3 PIN Mux Table Control Register for L2SW P0 & L2SW P0 (sft cfg 3)

Address: 0x9C00010C

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII TXD 0 SEL | 14:8 | RW | Layer 2 Switch P0 MAC RMII TXD0 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII TXEN SEL | 6:0 | RW | Layer 2 Switch P0 MAC RMII TXEN Pin-Mux Column Selection |

2.4 PIN Mux Table Control Register for L2SW P0 & L2SW P0 (sft cfg 4)

Address: 0x9C000110

Reset:0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII CRSDV SEL | 14:8 | RW | Layer 2 Switch P0 MAC RMII CRSDV PinMux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII TXD1 SEL | 6:0 | RW | Layer 2 Switch P0 MAC RMII TXD1 Pin-Mux Column Selection |

2.5 PIN Mux Table Control Register for L2SW P0 & L2SW P0 (sft cfg 5)

Address: 0x9C000114

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII RXD1 SEL | 14:8 | RW | Layer 2 Switch P0 MAC RMII RXD1 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII RXD0 SEL | 6:0 | RW | Layer 2 Switch P0 MAC RMII RXD0 Pin-Mux Column Selection |

2.6 PIN Mux Table Control Register for L2SW P0 & L2SW P1 (sft cfg 6)

Address: 0x9C000118

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII TXEN SEL | 14:8 | RW | Layer 2 Switch P1 MAC RMII TXEN Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P0 MAC RMII RXER SEL | 6:0 | Layer 2 Switch P0 MAC RMII RXER Pin-Mux Column Selection |

2.7 PIN Mux Table Control Register for L2SW P1 & L2SW P1 (sft cfg 7)

Address: 0x9C00011C

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII TXD1 SEL | 14:8 | RW | Layer 2 Switch P1 MAC RMII TXD1 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII TXD0 SEL | 6:0 | Layer 2 Switch P1 MAC RMII TXD0 Pin-Mux Column Selection |

2.8 PIN Mux Table Control Register for L2SW P1 & L2SW P1 (sft cfg 8)

Address: 0x9C000120

Reset: 0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII RXD0 SEL | 14:8 | RW | Layer 2 Switch P1 MAC RMII RXD0 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII CRSDV SEL | 6:0 | RW | Layer 2 Switch P1 MAC RMII CRSDV PinMux Column Selection |

2.9 PIN Mux Table Control Register for L2SW P1 & L2SW P1 (sft cfg 9)

Address: 0x9C000124

Reset:0x0

Field Name | Bit | Access | Description |

Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits |

reserved | 15 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII RXER SEL | 14:8 | RW | Layer 2 Switch P1 MAC RMII RXER PinMux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG L2SW P1 MAC RMII RXD1 SEL | 6:0 | RW | Layer 2 Switch P1 MAC RMII RXD1 PinMux Column Selection |

2.10 PIN Mux Table Control Register for L2SW P1 & DAISY MODE (sft cfg 10)

Address: 0x9C000128

Reset: 0x0

Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| reserved | 15 | RW | RESERVED |

| SFT CFG SDIO CLK SEL | 14:8 | RW | SDIO CLK Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG DAISY MODE SEL | 6:0 | RW | DAISY MODE Pin-Mux Column Selection |

2.11 PIN Mux Table Control Register for SDIO CLK & SDIO CMD (sft cfg 11)

Address: 0x9C00012C

Reset: 0x0

Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| reserved | 15 | RW | RESERVED |

| SFT CFG SDIO CMD SEL | 14:8 | RW | SDIO CMD Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG SDIO CLK SEL | 6:0 | RW | SDIO CLK Pin-Mux Column Selection |

2.12 PIN Mux Table Control Register for SDIO D0 & SDIO D1 (sft cfg 12)

Address: 0x9C000130

Reset: 0x0

Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| reserved | 15 | RW | RESERVED |

| SFT CFG SDIO D1 SEL | 14:8 | RW | SDIO D1 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG SDIO D0 SEL | 6:0 | RW | SDIO D0 Pin-Mux Column Selection |

2.13 PIN Mux Table Control Register for SDIO D2 & SDIO D3 (sft cfg 13)

Address: 0x9C000134

Reset: 0x0

Field Name | Bit | Access | Description |

| Mask Bits | 31:16 | RW | Write valid bit for each LSB 16 bits The 16 bits map to corresponding LSB 16bits. Write 1 to valid the corresponding bit writing |

| reserved | 15 | RW | RESERVED |

| SFT CFG SDIO D3 SEL | 14:8 | RW | SDIO D3 Pin-Mux Column Selection |

| reserved | 7 | RW | RESERVED |

| SFT CFG SDIO D2 SEL | 6:0 | RW | SDIO D2 Pin-Mux Column Selection |

2.14 PIN Mux Table Control Register for PWM0 & PWM1 (sft cfg 14)